# New Generation of Innovative Power gating on Embedded Systems

K.Vinoth<sup>\*1</sup>V.M.Padmapriya<sup>\*2</sup> Prist Universitypg Student ECE

#### Abstract

Multi threshold CMOS power gating is very effective for reducing static leakage power during long periods of inactivity. Power-gating method was used to provide multiple power off modes and reduce the leakage power during short periods of inactivity. This scheme can suffer from high sensitivity to process variations of logic. We propose a new power-gating technique that is tolerant to process variations and scalable to more than three intermediate power-of fmodes. The proposed design requires less design effort and provide large power reduction and smaller area cost than the previous method. In addition, it will be combined with existing methods to offer further static power reduction. Analysis and extensive simulation results demonstrate the effectiveness of the proposed design.

**Index words:** *multi-mode power switches, power consumption reduction, process variation, reconfigurable power-gating structure.*

# I. INTRODUCTION

Multi-threshold CMOS is a budding knowhow that provide high concert and low command function by utilizing both high and low Vt transistors. By low Vt transistors in the indication lane, the provide voltage can be lowered to diminish switching power indulgence. By dipping Vdd, the switching influence can be condensed quadratic ally, but as Vt decreases to continueroutine, the subentranceseepagecontemporary will increase exponentially. For ruthless scaling, the better outflow supremacy can really direct the switching power. Recently, several dealer goods in the low command fixed liberty offer power-gating bear in the appearance of "sleep" modes, typically software run. One of numerous super computer cores, in such as arrangement, runs at the greatest in use regularity and the other mainframe cores can be power-gated off when the working classification detects a elongate dinoperative loop. The destructive power-saving line of attack above, but, has the follow probable harms.

The scaling of development technologies to nanometer administration has resulted in a rapid make bigger in seepage power rakishness. Hence, it has befallen normously significant to extend devise techniques to diminish fixed cloutdebauchery all through periods of immobility. The power lessening must be achieved devoid of trading-off show which makes it harder to reduce leakage during normal operation. On the other hand, there are several techniques for reducing leakage power in sleep or standby mode. Power gating is one such well known technique where a sleep transistor is added between actual ground rail and circuit ground .This device is turned-off in the sleep mode to cut-off the leakage path. It has been shown that this technique provides a substantial reduction in leakage at a minimal impact on performance.

#### **II. RELATED WORK**

In [1] Y. Alkabani, T. Massey, F. Koushanfar, and M. Potkonjak et al presents enter vector organize is an efficient means to diminish the run away, as in the circuit's slumber circumstances, the seepageon hand muscularly depends on the stab vector blend this step is skilled using a novel fat locality iterative perfection (LNII) algorithm. Next, we classify related solutions and choice a small set of delegatesay vectors in such a way that any non-selected IC have at slightest one IC with a spokesperson participation surrounded by its specific Hamming disconnection. Leveraging on the somewhatminiaturebulk of the ambassador inputs and their arrangement, this quandary is optimally solve using figure linear encoding.

In [2] M. Chowdhury, J. Gjanci, and P. Khaled et al presents To appraise the efficacy of the authority gating techniques, the replication has been performed using BPTM 45nm knowledge at area hotness with bring incurrent of 0.7V. The chief brave for FPGAs implemented in nanometer CMOS technologies is the ever-increasing clout rakishness and in meticulous, leakage supremacy. Also, as we go behind to equipment opinion leap blast also suit important metric of analogous magnitude to vigorous supremacy, stoppage and vicinity for the psychoanalysis and intend of sequence operate strategy. Traditionally, seepage control decline in FPGAs has been overshadowed by a curiosity in tumbling the go-ahead power uprightness and humanizing the generally recital.

In [3] H. Kawaguchi, K. Nose, and T. Sakurai et al presents the pMOSs in the reason circuits can as

well split the healthy with the cut-off pMOSs. In this holder however, an extra virtual line must be added to the cell libraries. Similarly, an nMOS inclusion case is also attainableby an extra virtual land procession to the cubicle libraries. A further format called variablethreshold CMOS applies back-gate foregone wrapping up to cut off escape modern in a stand-by mode by exploit body consequence. This format cannot be functional to copious exhausted SOI progression knowledge. It is also complicated to relate to incompletely useless SOI development expertise out standing to the transparency mandatory to unite the remains of both MOSFET with interconnection for applying the carcass bias.

In [4] K.-S.Min, H.-D.Choi, H.-Y. Choi, H. Kawaguchi, and T. Sakurai et al presents . A clockgating proxy is projected which achieves a 200ps wakeup point and 3 information of size see page lessening for leaching overriding LSI's and experimentally verifies the usefulness of the method. Voltages are in general not conventional, since they are resolute by the last inputs to the wedge. To formulate each node energy humdrum, a fresh phase-forcing path is further to the key in F/F depicted where P and O are mandatory to be low or lofty even nevertheless D is mysterious during sleep. Without input phase forcing, the internal node voltages of the hunk may be shifting from H to L or L to H all through sleep. When the come around signal comes, if the domestic bump voltages are in stuck amid VDD and VSS, a hefty short-circuit climax current may crop up and bulkyrousestop pages keleton the proposal.

In [5] P. Heydari and M. Pedram et al presents A number of researchers have studied the influence and land spring back dilemma. The P/G pounce back noise is the switching noise on the power-supply and earth lines which consists of the resistive IRplunge due to bond cable and trace resistances, inductive noise due to the chip-package edge inductance as well as bond lead self-inductance, outline self inductance, trace-to-trace shared inductance, and capacitive combination due to the chip-package boundary crosscoupling capacitances. While, due to circuit innovations and device scaling, the speed and accuracy of incorporated circuits have steadily augmented, the recital of packages, mainly for low-cost application, has not drastically improved.

## III. MULTIMODE POWER-GATING ARCHITECTURE

The offered makeup requires least design endeavor seeing as it is exceedingly undemanding, and among no analog machinery. It is very much slighter than the planning accessible and offers superior control reserves for like awaken period. The projected construction is also added liberal to course variations; thus its action is more conventional. In vacant means four methods are there. In this methods are

- Active Mode

- Snore Mode

- Dream Mode

- Sleep Mode

- A. Active Mode

- Transistors MP, M0, M1 are on

- B. Snore Mode

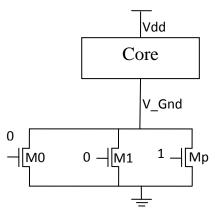

#### Fig.1 Snore Mode

- Transistors MP, M0, and M1 are off

- The escapetopical of the nucleusI Lcore, is the same to the amassedflightmodernelegantthroughout transistors M0, M1, MP (I Lcore = I LM0 + I LM1 + I LMP), which is very minute.

- The powerplane at V\_GND is secure to Vdd and the course consumes a smalltotal of vigor, but the wake-up instance is elevated.

#### C. Dream Mode

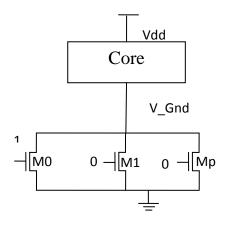

- Transistor M0 is on and transistors MP and M1 are off.

- In this holder, the contemporary smooth during transistor M0 (and thus the combined up to datesmoothall the way throughM0, M1, and MP) increases asM0 is on (IM0 > I LM0).

- The exact value of IM0 depends on the size of transistor M0, and it sets the virtual ground node at a voltage level which is lower than Vdd (i.e., VV\_GND <Vdd). Thus the static power consumed by the core is higher compared to the snore mode, but the wake-up time is less.

Fig.2 Dream Mode

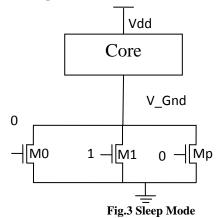

D. Sleep Mode

- Transistor M1 is on, and MP, M0 are off

- The transistor M1 has larger aspect ratio than M0 (WM1/LM1 > WM0/LM0), the aggregate current flowing through M0, M1, and MP increases even more when M1 is on (note that IM1 > IM0).

- Consequently, the voltage level at the virtual ground node is further reduced compared to the

- Dream mode and thus the wake-up time decreases at the expense of increased power consumption.

# **IV. IMPLEMENTATION**

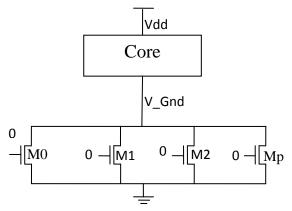

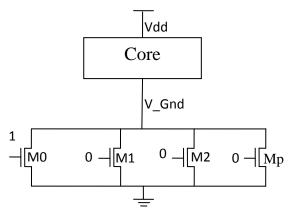

Four power-off modes are present. It consists of four footer transistors MP, M0, M1 and M2 that are connected between the core and the ground rail. The main power switch MP is a large high-Vttransistor, and it is implemented using several smaller transistors connected in parallel. Transistors M0, M1 and M2 are very small low-Vttransistors. A. Snore Mode

#### **Fig.8 Snore Mode**

- The virtual ground rail (V\_GND) charges to a voltage level VSnoreclose to the power-supply.

- The leakage currents of the transistors of the circuit are suppressed. In this mode the leakage current of the core, ILcore, is equal to the aggregate leakage current flowing through transistors M0, M1, M2, MP (ILcore= ILM0 + ILM1 + ILM2 + ILMP), which is very small.

- Thus, the voltage level VSnoreat virtual ground rail VV\_GND approaches Vddand the circuitconsumes a negligible amount of energy.

In order to restore the voltage of the virtual ground rail to its nominal value when the circuit transitions from the power-off mode to the active mode, the parasitic capacitance at the V\_GND node has to be completely discharged through the power switch MP which is turned-on again. However, the aggregate size of the transistors comprising the power switch MP is relatively small compared to the size of the core and thus it cannot quickly discharge the V\_GND node. Thus the wake-up time can be long relative to circuit clock period, and MP cannot be turned-off during short periods of inactivity.

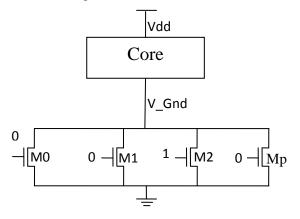

# B. Dream Mode

Fig.9 Dream Mode

- The current flowing through transistor M0 increases compared to the snore mode because M0 is on (IM0 > ILM0).

- The exact value of IM0 depends on the size of transistor M0, and it sets the V\_GND node at a voltage level VDreamwhich is lower than that of the snore mode (VDream<VSnore).

- Thus the static power consumed by the core increases compared to the snore mode, but the wake-up time drops.

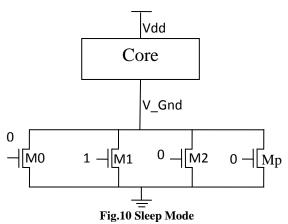

#### C. Sleep Mode

- The sleep mode is implemented by decreasing the voltage level at the virtual ground node.

- This is achieved by using transistor M1 which has larger aspect ratio than M0 (WM1/LM1 > WM0/LM0).

• When only M1 is turned-on the aggregate current flowing through M0, M1, and MP increases even more and the voltage level VSleepat the virtual ground node is further reduced compared to the dream mode (VSleep<VDream<VSnore).

• The wakeup time decreases at the expense of increased static power consumption, which however, remains much lower than the static power of the active mode.

# D. Nap Mode

- The "nap" mode is implemented by further increasing the aspect ratio of the respective power switch (i.e., WM2/LM2 >WM1/LM1 > WM0/LM0).

- In nap mode the voltage level at V\_GND node is set at VNap, where VNap<VSleep<VDream<VSnore.

- The static power consumption increases and the wake-up time reduce even more.

Fig 11 Nap Mode

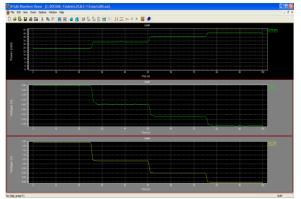

## V. SIMULATION RESULT

The system can be implemented using Tanner EDA tool. A  $4\times4$  multiplier circuit can be used as a logic circuit and ground of logic can be connected on the Power switches. Various mode of operation can be simulated and its ground voltage can be calculated.

| simulated and its ground voltage can be calculated. |            |            |       |

|-----------------------------------------------------|------------|------------|-------|

|                                                     | Mode       | Ground     | Power |

|                                                     |            | voltage(v) | (mW)  |

|                                                     | Snore Mode | 1.85       | 25    |

|                                                     |            |            |       |

|                                                     | Sleep Mode | 1.65       | 33    |

|                                                     | Nap Mode   | 0.95       | 37    |

|                                                     | Dream Mode | 0.45       | 44    |

**Fig.11 Simulation Result**

## **VI. CONCLUSION**

One of the main lively authority patrons in computing and customer electronics harvest is the system's regulator gesture, classically liable for 30% to 70% of the entirety go-ahead (switching) power using up The embedding of LACG reason in the RTL practical policy is exceptionally definite and easily resulting from the innovative judgment, disjointedly of the ambition claim. This overview is useful as it drastically simplifies the gating accomplishment. Lookahead regulator gating has been given away to be very positive in falling the clock switching run. To make use of the capability treasury, the FFs must to be grouped such that their toggling is plainly dependable. These require in a line upwidespread simulations characterizing the emblematic applications probable by the end-user. The totaling of the clock enabling signals one sequence in advance of instance avoids the stretched timing constraints offered in other gating methods. А congested form representation characterizing the power economy was accessible and worn in the triumph of the gating logic. The gating judgment can be supplementary optimized by matching objective FFs for dual gating which may considerably lessen the hardware expenditure.

## REFERENCE

[1] Semiconductor Industry Association. (2007) [Online]. Available:

http://www.itrs.net/Links/2007ITRS/Home2007.htm

- [2] D. Lackey, P. Zuchowski, T. Bednar, D. Stout, S. Gould, and J. Cohn, "Managing power and performance for system-on-chip designs using voltage islands," in Proc. IEEE/ACM Int. Conf. Comput. Aided Design, Nov. 2002, pp. 195–202.

- [3] R. Puri, D. Kung, and L. Stok, "Minimizing power with flexible voltage islands," in Proc. IEEE Int. Symp. Circuits Syst., May 2005, pp. 21–24.

- [4] R. Puri, L. Stok, J. Cohn, D. Kung, D. Pan, D. Sylvester, A. Shrivastava, and S. Kulkarni, "Pushing ASIC performance in a power envelope," in Proc. Design Autom. Conf., Jun. 2003, pp. 788–793.

- [5] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deepsubmicrometer CMOS circuits," Proc. IEEE, vol. 91, no. 2, pp. 305–327, Feb. 2003.

- [6] S. Idgunji, "Case study of a low power MTCMOS based ARM926 SoC: Design, analysis and test challenges," in Proc. IEEE Int. Test Conf., Oct. 2007, pp. 1–10.

- [7] A. Abdollahi, F. Fallah, and M. Pedram, "Leakage current reduction in CMOS VLSI circuits by input vector control," IEEE Trans. Very LargeScale Integr. (VLSI) Syst. vol. 12, no. 2, pp. 140–154, Feb. 2004.

- [8] Y. Alkabani, T. Massey, F. Koushanfar, and M. Potkonjak, "Input vector control for post-silicon leakage current minimization in the presence of manufacturing variability," in Proc. 45th ACM/IEEE Design Autom.Conf., Jun. 2008, pp. 606–609.

- [9] K. Kim, Y.-B. Kim, M. Choi, and N. Park, "Leakage minimization technique for nanoscale CMOS VLSI," IEEE Des. Test Comput. vol. 24, no. 4, pp. 322–330, Jul. 2007.

- [10] S. Mukhopadhyay, C. Neau, R. Cakici, A. Agarwal, C. Kim, and K. Roy, "Gate leakage reduction for scaled devices using transistor stacking," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 11, no. 4, pp. 716–730, Aug. 2003.