# Realization of BIST Architecture using SRAM Cell Based on Input Vector Monitoring

Miruthubashini.S<sup>1</sup>,Venkatesan.K<sup>2</sup>, Kirubakaran.T<sup>3</sup> <sup>123</sup>(Department of ECE, Sri Shakthi Institute of Engineering & Technology, INDIA)

#### Abstract

To perform testing during normal operation of the circuit, without forcing the circuit to go offline is concurrent BIST testing. Built-In Self Test (BIST) techniques constitute an attractive and practical solution, to solve the problem of testing VLSI circuits and systems. In this paper, we perform input vector monitoring BIST scheme, by monitoring a set of vectors called windows during its normal operation and the testing of the circuit is also carried on along with its normal operation of the circuit.

**Keywords** – *BIST*, *CUT*, *Concurrent*, *Input Vector Monitoring*, *Online BIST*.

#### I. INTRODUCTION

In recent years, the advent of VLSI, has increased the complexity of digital circuits at an exponential rate. Increased circuit complexity also complicates the testing problem. A device is tested at different stages of manufacturing and hence it is a continual problem. It must undergo an acceptance test before it is integrated into a system .To ease testing, two new disciplines have emerged namely, design for testability (DFT) and BUILT-IN Self Test (BIST).Both these disciplines require adding extra logic to alleviate the testing problem. In DFT environment, the extra logic is active during the test mode(off-line)operation of a logic circuit and such logic is idle during normal operation of the circuit .BIST techniques, can be used either for on-line or off-line. The introduction of nanotechnologies and SOC devices brings forth new problems in semiconductor memory testing.So researchers have been attracted towards BIST architecture due to it ease toward testing. The use of BIST circuits and other embedded instruments is becoming more prevalent as devices become larger, faster, and more complex. These instruments can increase the device's test coverage, decrease test and debug time, and provide correlation between the system and ATE environments. Examples of some of these instruments are logic BIST, memory BIST (for both internal and memory), bit-error-rate external testing for serializer/deserializer (SerDes), power management and clock control logic, and scan register dump capabilities.

## II. BIST TECHNIQUE

Built-In Self Test is a practical solution to provide the system with an attractive test solutions. BIST is an in built set up to provide the system with an effective and economic way to find the effectiveness of the system. For this testing BIST constitutes two types of modes on-line and off-line mode. Periodic testing of IC is done at system level should be done, to prevent accumulation of faults. Such periodic testing is done off-line that is system is stopped and tested using a set of vectors. But off-line mode provides a performance degradation since it affect the normal operation of the circuit. On-line mode is testing the Circuit, during its normal operation without going into off-line mode.there by it increases its performance and efficiency. On-line BIST uses normally occurring data as inputs and employs redundancy techniques to do concurrent checking. Concurrent means testing occurs simultaneously with normal functional operation (Realized by using coding techniques) and Nonconcurrent means testing is Carried out while in idle state.

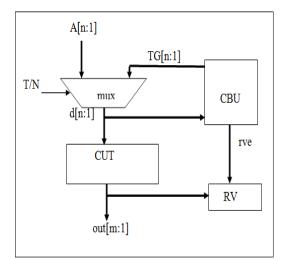

Figure 1.1: Input Vector Monitoring Concurrent BIST

### III. PROPOSED ARCHITECTURE WITH INPUT VECTOR MONITORING

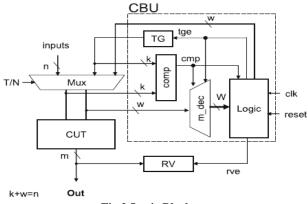

In the proposed architecture , a modified decoder and an SRAM logic block is used.A decoder has been modified by applying comparator signals and test generator enable signals with implementation of and gate and or gate.The decoder will have w inputs and W outputs with control signals, comparator and test generator enable.

#### IV. MODULE DESCRIPTION

The BIST module has CUT, Mux, Response Verifier(RV) and Concurrent BIST Unit(CBU).In CBU it consists of sub-modules of Logic, Comparator , Modified decoder, Test Generator(TG) each one of the block is explained in detail in the below passages. Mux: The data multiplexer of the BIST architecture select whether normal mode or test mode(BIST provided inputs). It act as a control element or as a switch ,indicating in which mode the circuit should operate, depending on the value of the signal labeled T/N.

Circuit Under Test (CUT): Circuit under test (CUT) can be the entire chip or only a part of the chip (e.g., a memory core or a logic block). Input test vectors are binary patterns applied to the inputs of the CUT and the associated output responses are the values observed on the outputs of the CUT. The CUT has n inputs and m outputs and is tested exhaustively hence the test set size is  $N=2^n$ .

Concurrent BIST Unit (CBU): CBU consists of sub–blocks of TG, Comparator, Decoder and Logic circuits.Test Generator: It is a test pattern generator module which receives its input from Logic module and its output is driven to mux.To provide the input vectors, generated from CBU.Comparator: It compares the outputs of test generator and Mux and provide its output to decoder and Logic. When the the output of the decoder is enabled ,the decoder module operates as a normal decoding structure.Response Verifier: The Response verifier stores the result of CUT and Logic .Once when the circuit attain all the hits ,the results in the response verifier are viewed latter.

#### V. FUNCTIONALITY OF THE PROPOSED ARCHITECTURE

The select line of mux T/N will decide whether the module will work in test mode or normal mode.If Test mode means, the inputs for the CUT are generated from the output of CBU denoted as TG[n:1].Test Generated module.If ,normal mode means the inputs for the CUT are generated by A[n:1].For both the mode the responses are captured in the response verifier(RV). The Circuit Under Test has n inputs, m outputs and is tested exhaustively. The test set size for the CUT is N = 2n. The BIST module consists of a CUT which is combinational with n input line, a Mux to determine whether to operate it in test mode or normal mode, a CBU and a RV to capture the responses of CUT with its corresponding . The basic idea is of monitoring a window of vectors, of size W , which is W=2w, where w is an integer w < n.The input vector n is divided into two parts w and k,in which k is the higher order and the remaining w bits show the location of the current window.The vectors in the current window are monitored ,and if a vector performs a hit,RV is enabled. Once the vectors in the current window are monitored,then it goes to the next window.w bits are given to the modified decoder with the functionality as ,When tge is 1 ,all the output will be enabled.If cmp is disabled and tge is disabled then all the outputs will be disabled.when cmp is enabled and tge is disabled then the circuit will operate in normal mode.

Fig 2:Logic Block

#### VI. OPERATION OF LOGIC MODULE

The logic module consists of W cells (operating like SRAM cell), an amplifier(sense), then two D flip-flops, and a w-stage counter (where w = log2W). The tge signal was triggered by a unit flip-flop delay by the overflow signal of the counter. The clock signals(clk and clock) are enabled during the active low and high of the clock, respectively.

The functionality of the logic module can be explained in a set of five operations ,first need to reset the module ,then hit of the vectors are monitored whether they reached the windows already or they are appearing for the first time and then the tge operation is monitored .

The module is reset by an external reset signal. Once the reset was triggered, the tge signal is enabled and all the outputs of the decoder are enabled. So, DA1,DA2, ..., DAW are one and the  $CD_{-}$  signal is enabled; therefore, a one is written to the right hand side of the cells and a zero value to the left hand side of the cells.

Then the hit of the vector is being monitored.During normal mode, the inputs to the CUT are taken from the normal inputs. The n inputs are also driven to the CBU as follows: the w loworder inputs are driven to the inputs of the decoder; the k high-order inputs are driven to the inputs of the comparator. When a vector belonging to the current window reaches the inputs of the CUT, the comparator is enabled and one of the outputs of the decoder is enabled.

During the first half of the clock cycle (clk\_ and cmp are enabled) the addressed cell is read; because the read value is zero, the w-stage counter is triggered through the NOT gate with output the response verifier enable (rve) signal. During the second half of the clock cycle, the left flip-flop (the one whose clock input is inverted) enables the AND gate (whose other input is clk and cmp), and enables the buffers to write the value one to the addressed cell.If the cell corresponding to the incoming vector contains a one (i.e., the respective vector has reached the CUT inputs during the examination of the current window before). The rve signal is not enabled during the first half of the clock cycle; hence, the w-stage counter is not triggered and the AND gate is not enabled during the second half of the clock cycle.

When all the cells are full (value equal to one), then the w-stage counter is all one. Hence, the activation of the rve signal causes the counter to overflow; hence in the next clock cycle (through the unit flop delay) the tge signal is enabled and all the cells (because all the outputs of the decoder are enabled) are set to zero.When switching from normal to test mode, the w-stage counter is reset. During test mode, the w-bit output of the counter is applied to the CUT inputs. The outputs of the counter are also used to address a cell. If the cell was empty (reset), it will be filled (set) and the RV will be enabled. Otherwise, the cell remains full and the RV is not enabled.

Once when these operations are completed the output from the logic module is stored in the RV where the output of the CUT are compared with the logic output

#### SIMULATION RESULTS VII.

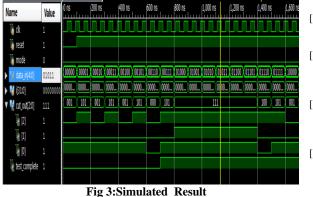

The verilog HDL coding and simulation of the design are done in Xilinx tool ISim 14.4.The simulated output of BIST architecture using Input vector monitoring is faster than its previous[1-7] results.It is been displayed with timing diagram of the logic and SRAM cells.

VIII.

proposed scheme achieves shorter CTL than other schemes.Like,in terms of hardware overhead the proposed scheme is 16% less number of gates than SWIM and 33% less number of gates than w-MCBIST. It resulted that decrease in hardware overhead obtains higher as the CTL decrease. The result show that the proposed scheme is more efficient than the existing system with in terms of hardware overhead and CTL.

CONCLUSION

simulated results for input vector monitoring BIST architecture using SRAM -cell like structure for

storing the information of whether an input vector has

appeared or not during normal operation. The result

shows that ,with the same hardware overhead, the

In this paper, it present an Xilinx ISE

#### REFERENCE

- [1] Almukhaizim S.,and Makris Y.,(2007)"Concurrent error detection methods for asynchronous burst mode machines," IEEE Trans. Comput., vol. 56, no. 6, pp. 785-798.

- [2] Almukhaizim S., Drineas P., and Makris Y.,(2006) "Entropy-driven parity tree selection for low-cost concurrent error detection," IEEE Trans. Comput. Aided Design Integr. Circuits Syst., vol. 25, no. 8, pp. 1547-1554.

- Al-Asaad H., and Shringi M.,(2000) "On-Line Built-In Self-Test for Operational Faults," Proc. of Conf. [3] Systems Readiness Technology, pp.168-174.

- [4] Abramovici M., Breuer M., and Friedman A.,( 1990.) "Digital Systems Testing and Testable Design," Computer Science Press, New York.

- Bardell P. H., McAnney W.H., and Savir J., Built-In [5] Test for VLSI: Pseudorandom Techniques. John Wiley & Sons, Inc, New York.

- [6] Chandel R., and P. Daniel(2011), "Concurrent Online Test Architecture for Multiple Controller Blocks with Minimum Fault Latency," Ninth IEEE International Symposium on Parallel and Distributed Processing with Applications Workshops, pp.45-49, 26-28.

- Gizopoulos D., Halatsis C., Kranitis N., Paschalis A.,and Voyiatzis I.,(2005) "A concurrent BIST [7] architecture based on a self testing RAM," IEEE Trans. Rel., vol. 54, no. 1, pp. 69-78.

- Halatsis C., and Voyiatzis I.,(2005) "A low-cost [8] concurrent BIST scheme for increased dependability,' IEEE Trans. Dependable Secure Comput., vol. 2, no. 2, pp. 150-156.

- [9] Huang L. R., Jou J. Y., and Kuo S. Y.,(1997) "Gausselimination based generation of multiple seedpolynomial pairs for LFSR," IEEE Trans. Comput. Aided Design Integr.Circuits Syst., vol. 16, no. 9, pp. 1015-1024.

- [10] Ivanov A., and Zorian Y.,(1992) "An effective BIST scheme for ROM's,"IEEE Trans. Comput., vol. 41, no. 5, pp. 646-653.

- [11] I. Voyiatzis, T. Haniotakis, C. Efstathiou, and H. Antonopoulou,(2010) "A concurrent BIST architecture based on monitoring square windows," in Proc. 5th Int. Conf. DTIS, pp. 1-6.

- Kime C. R., Saluja K. K., and R. Sharma,(1988) "A [12] concurrent testing technique for digital circuits," IEEE Trans. Comput. Aided Design Integr. Circuits Syst., vol. 7, no. 12, pp. 1250-1260.

- [13] Kime C. R., Saluja K. K., and R. Sharma.,(1986) "Concurrent comparative built-in testing of digital Univ. circuits," Dept. Electr. Comput. Eng., Wisconsin, Madison, WI, USA, Tech. Rep. ECE-8711. Kochte M. A., Wunderlich H.-J., [14] and C.

- Zoellin.,(2009) "Concurrent self-test with partially

specified patterns for low test latency and overhead," in Proc. 14th Eur. Test Symp., pp. 53-58.

- McCluskey E. J.,(1985) "Built-in self-test techniques," [15]

- IEEE Design Test Comput., vol. 2, no. 2, pp. 21–28. R. Sharma and K. K. Saluja, (1993)"Theory, analysis [16] and implementation of an on-line BIST technique," VLSI Design, vol. 1, no. 1, pp. 9-22.

- Rajski J., and Tyszer J.,(1993) "Test responses [17] compaction in accumulators with rotate carry adders," IEEE Trans. Comput. Aided Design Integr. Circuits

- Syst., vol. 12, no. 4, pp. 531–539. Stroud C.,( 2002) "A Designer's Guide to Built-In Self-Test," Kluwer Academic Publishers, Boston Voyiatzis I., (2008), "On reducing aliasing in [18]

- [19] accumulator-based compaction,"in Proc. Int. Conf. DTIS, pp. 1–12.

- [20] Wolf W.,(2002) "Modern VLSI Design: System-on-Chip Design," Prentice Hall, New Jersey.