# Fault Tolerant Parallel Filter in Digital Communication Systems

Jyotishma Bharti#1, Tarana Afrin Chandel#2

#1M.TECH Student, #2Associate Professor, 1,2Department of ECE, Integral University, Lucknow, INDIA

#### Abstract:

There are various types of filters are used by Digital signal processing (DSP) applications. In which digital parallel FIR filters are very widely used in numerous application. Over the years, many implementation techniques of digital FIR filter for DSP application has exploited the various practical difficulties such as low speed, high delay and above of all fault tolerance. Due to the VLSI complexity scaling, there are many complex systems that embed with many filters. The filters operations in those complex systems are usually parallel. As filters are the unit that comes in any type of communication system ranging from simple voice data to complex real-time data conversation. So it is then mandatory to implement some technique that shows the fault tolerance achieved in parallel filters. In this paper, we are going through various ideas that show that parallel filters can be protected using error correction codes (ECCs).

**Keywords:** Error Correction Codes (ECC), Digital Signal Processing (DSP), Finite Impulse Response (FIR) Parallel FIR, Very Large Scale Integration (VLSI).

# I. INTRODUCTION

The demand for high performance and low power DSP is getting exponentially higher due to the bombardment of multimedia application such as automotive, medical and space applications where reliability is critical. And in those specific applications, the electronic circuits should have to provide some degree of fault tolerance. Although there are various other techniques that can be used to protect a circuit from errors. These errors can be removed ranging from modifications in the manufacturing process of the circuits for reducing the number of errors by adding redundancy bits at the logic or system level in order to ensure that these errors can do not affect the system functionality.

As in this paper, we are more focusing on Filter processing so it is mandatory to emphasize on the application area of Filters. The filters are the basic unit of any type of communication. In the basic communication system, the transmission of information/raw data is not always free from unwanted information bits or Noise. Thus it is very necessary for any communication systems to must have appropriate means for the finding and correction of errors in the information received over any communication channels. This paper deals with the study of the use of the various Error corrections coding scheme into Digital FIR Filter design.

# II. ERROR CORRECTING CODES- AN OVERVIEW

During the Digital communication system, the information always travels through a medium. And the transformation of the information through this channel could not always be free from noise. Also, we know that in digitally encoded data, there is a series of symbols denoted generally in the terms of Os and 1s. Suppose that we want to transmit the information that "There is no class on Monday". This information can be defined by 01101111, say, and transmitted over a channel where some unwanted data i.e. "noise" may be introduced. Noise means simply errors. By error, we mean that there is an unwanted change in data which is required to be correct for efficient and reliable reception of data. following diagram The represents the

communications channel.

Fig 1: Basic Communication System

An error is a change or the mismatching takes place between the data unit sent by the transmitter and the data unit received by the receiver e.g. 10101010 sent by sender 10101011 received by the receiver. Here is an error of 1 bit. Error control refers to mechanisms to detect and correct errors that occur in the transmission of the frame. There are various techniques available for error control but the basis of all error detection and correction is the inclusion of redundant information.

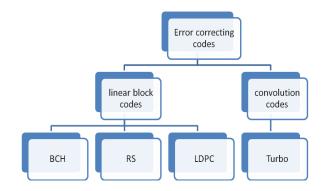

Fig2: Classification of Error Correcting Codes

# **III. PARALLEL FILTER**

A discrete time filter follows the following equation:

$$y[n] = \sum_{l=0}^{\infty} x[n-l] \cdot h[l]$$

.....(1)

As stated in equation 1, x[n] is the input signal, y[n] is the output, and h[l] is the impulse response of the filter. The FILTERS has been categorized by this impulse response. For a FIR FILTER the response h[l] should be nonzero, only for a finite number of samples. Otherwise the filter is an infinite impulse response (IIR) filter. There are several structures to implement both FIR and IIR filters.

Fig 4: Digital Filter

We can also cascade n number of filters in a single communication systems.

#### IV. PROPOSED BLOCK DIAGRAM

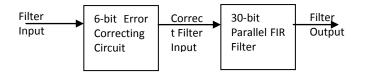

In this work we are generating a Self error detector and corrector for FIR Filter. We are integrating two different topologies into a one solution. The proposed block diagram is shown in figure 3.

#### Fig 3: Proposed Block Diagram

The figure 3 shows the proposed schematic for our research work. The filter input first propagates through the error detection and correction circuit. Then the output from the error correcting detecting circuit will finally go to the parallel FIR filter.

# V. SYNTHESIS & SIMULATION RESULTS

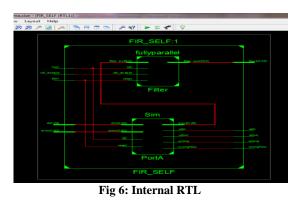

This section shows the various results obtained from the XILINX ISE Tool. The figure 6 & 7 shows the RTL view of our designed circuit i.e. Fault tolerant FIR Filter. As shown in the figure there are two inputs named as A, and error. The input A denotes the original message to be filter through the FIR filtration. While error signal are for stimulating the various number of errors.

Fig 5: RTL for Fault Tolerant FIR

The figure 5 shows only the input output ports which can be used as a physical interface for real world implementation. On the other hand figure 6 shows the internal structure of the Fault tolerant FIR filter. In this two separate block has been connected together to achieve the desired output.

The figures 7, 8 shows the cumulative result for the fault tolerant fir filter with different input conditions.

Fig 7: Simulation Result with initial Conditions.

The figure 7 shows the simulation results with initial conditions i.e. RST='1'. For initialization of all the registers, signals into its original states/values.

Fig 8: Simulation Results with 4 bit Error Correction

The figure 8 shows the result with stimulation of 4 bit error values through error signal. And we can easily observe that there is not a slight change in the output waveform.

### VI. CONCLUSION

During our research, I observed from the literature discussed in the previous section that there are five primary criteria: area, speed, energy dissipation per bit, latency and error performance gap from the Shannon limit that must be considered in a BCH decoder design based on the application requirement. Current research has focused on the decoding algorithm, code design and VLSI implementation to meet the demands e.g. Less error, hardware reconfigurability, very high throughput and high efficiency. Although significant development on both construction and implementation of BCH codes has occurred in the past several years, the efficient realization of high-speed BCH decoders still remains challenge for ever-increasing high-speed а applications. Now we are going further to design our work i.e. using efficient coding scheme for faulttolerant FIR Filter. Although FIR Filters can also be made using different structures i.e. Parallel, Serial and each design has the common feature i.e. the multiplication and shifting process which requires lots of hardware area, so we are planning to reduce the hardware area by using Distributed Arithmetic structure. Our work will do require the Xilinx ISE tool for implementation of FIR Filter with Fault tolerant features.

#### REFERENCES

- P. P. Vaidyanathan, Multirate Systems and Filter Banks, Englewood Cliffs, N.J., USA: Prentice Hall, 1993.

- [2] A. Sibille, C. Oestges and A. Zanella, MIMO: From Theory to Implementation, New York, NY, USA: Academic, 2010.

- [3] N. Kanekawa, E. H. Ibe, T. Suga, and Y. Uematsu, Dependability in Electronic Systems: Mitigation of Hardware Failures, Soft Errors, and ElectroMagnetic Disturbances, New York, NY, USA: Springer-Verlag, 2010.

- [4] M. Nicolaidis, "Design for soft error mitigation," IEEE Trans. Device Mater. Rel., vol. 5, no. 3, pp. 405–418, Sep. 2005.

- [5] C. L. Chen and M. Y. Hsiao, "Error-correcting codes for semiconductor memory applications: A state-ofthe-art review," IBM J. Res. Develop.vol. 28, no. 2, pp. 124–134, Mar. 1984.

- [6] A. Reddy and P. Banerjee "Algorithm-based fault detection for signal processing applications," IEEE Trans. Comput., vol. 39, no. 10, pp. 1304–1308, Oct. 1990.

- [7] T. Hitana and A. K. Deb, "Bridging concurrent and nonconcurrent error detection in FIR filters," in Proc. Norchip Conf., 2004, pp. 75–78.

- Conf., 2004, pp. 75–78.

[8] Y.-H. Huang, "High-efficiency soft-error tolerant digital signal processing using fine grain sub word-detection processing," IEEE Trans. Very Large Scale

- [9] Integr. (VLSI) Syst., vol. 18, no. 2, pp. 291–304, Feb. 2010.

[9] Yu-Chi Tsao and Ken Choi, 2012. "Area- Efficient Parallel FIR Digital Filter Structures for Symmetric Convolutions Based on Fast FIR Algorithm" IEEE transactions on very large scale integration (VLSI) Systems, vol. 20, no. 2, Feb. 2012.

- [10] Yu-Chi Tsao and Ken Choi, 2011. "Hardware-

- Efficient Parallel FIR Digital FilterStructures For Symmetric Convolutions "978-1-4244-9474- 3/11/\$26.00 ©2011 IEEE.

- [11] Lavina Magdalene Mary "Area Efficient Parallel Fir Digital Filter Structures Based On Fast Fir Algorithm" Vol. 3, Issue 1, January –February 2013, pp.2042-2046

- [12] D. A. Parker and K. K. Parhi, 1997. "Low area/ power parallel FIR digital filter implementations," J. VLSI Signal Process.Syst., vol. 17, no. 1, pp. 75–92, 1997.

- [13] K. K. Parhi, VLSI Digital Signal Processing Systems: Design and Implementation.New York: Wiley, 1999.

- [14] J. G. Chung and K. K. Parhi, 2002. "Frequency spectrumbased low-area low-power parallel FIR filter design," EURASIP J. Appl. Signal Process., vol. 2002, no. 9, pp. 444–453, 2002.

- [15] Alfredo Rosado-Muñoz and Manuel Bataller-Mompeán, "FPGA Implementation of an Adaptive Filter Robust to Impulsive Noise: Two Approaches," vol.58, no.3, Mar.2011.

- [16] Z.-J. Mou and P. Duhamel, 1991. "Short-length FIR filters and their use in fast nonrecursive filtering," IEEE Trans. Signal Process., vol. 39, no.6, pp. 1322–1332, Jun. 1991.

- [17] C. Cheng and K. K. Parhi, 2004. "Hardware-efficient fast parallel FIR filter structures based on iterated short Convolution," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 51, no. 8, pp. 1492–1500, Aug. 2004.

- [18] C. Cheng and K. K. Parhi, 2005. "Further complexity reduction of parallel FIR filters," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS 2005), Kobe, Japan, May 2005.