# Different parameter analysis for SRAM

Vartika Pandey<sup>1</sup>, Manisha Pattaniak<sup>2</sup>, R K Tiwari<sup>3</sup>

<sup>1</sup>JiwajiUniversity, Gwalior, <sup>2</sup>ABV-IIITM, Gwalior, <sup>3</sup>Jiwaji University, Gwalior

Abstract: In today's VLSI design circumstances, upscaling of technology and downscaling of transistors are inversely proportional. Power dissipation impactsSRAM cells widely as the technology shrinks down. Static Random Access Memory (SRAM) is designed to interface with CPU directly, DSP processors, µprocessors, and lowpower applications such as handheld devices with long battery life. In the total power consumption, leakage and other parameters also play an important role in the circuit's performance. In this paper, we have applied two diverse technologies on 6 T SRAM, and the result has been comparedwith6T SRAM formed with memristor.

**Keywords:** SRAM, DTMOS, Memristor, Sleep transistor

## **INTRODUCTION**

Due to the endless escalation of MOSFET technology, the component diameter of integrated circuits faces many physical constraints. In integrated circuits, excessive leakage current and device/circuit reliability are the two major factors in the scaled devices. Power efficiency and reliability are conflicting issues that have been considered, especially for reliable circuit designs [1].

In the integrated circuits, the transistors suffer multiple temporal degenerations such as Hot Carrier Injection (HCI), Time-Dependent Dielectric Breakdown (TDDB), Bias Temperature Instability (BTI). This may cause significant discrepancies in the devices because of:-

(i) the improper manufacturing process, (ii) improper biasing, and (iii) improper working environmental conditions during their operation, resulting in degradation of device performance with time.[2]-[3].

Transistors also suffer from Process, Voltage, and Temperature (PVT) variations, which cause suspicion in VLSI integrated circuits. The reliability of the circuit degrades due to processing variation, such as variation in channel length, oxide thickness. [4]

With the progression of technology, SRAM has become an important component of technology scaling since chip area can be shrunk to a large extent in the memory for high-performance applications [5-6]. In modern technology, due to the continuous enlargement of nanoscale range devices, power consumption and packaging density have become the main restrictions in many designs. More than 40% of total active mode power is due to leakage current in high-performance I.C.s, though it is the only source of power consumption in idle circuits. Shortly, SRAM will likely be the preferred memory in embedded technology for various microprocessors and Systems on Chips(SoC) because of its speed and compatibility with typical logic processes. Variations in device geometry are based on threshold voltage due to dopant fluctuations and also on various fabrication processes and variations in it. These are most prominent in SRAM as the cell size is minimized using a width of devices and minimized gate length. The cell stability, which furnishes minimum array operation voltage and yield, is of primary concern and has become more difficult to focus on [7-8]. The design of power-efficient SRAM has become the principal factor in scaled technology of the modern era.

## A. 6T-SRAM

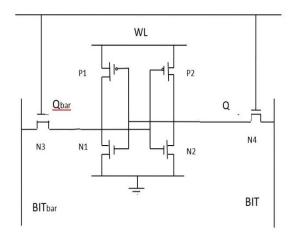

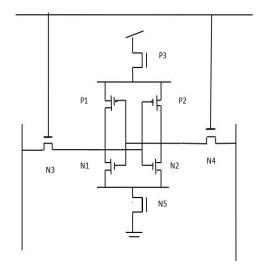

Fig. 1 shows the conventional 6T-SRAM cell. It consists of two CMOS inverters, which are crosscoupled with each other. During read and write operations, transistors are connected to the word line to activate read and write operations. In the active mode, the first-word line gets activated and is turned ON for access transistors to read data from the memory cell to write data on the memory cell through the bit line. During all read/write processes, power dissipation takes place. There are three types of operation taking place in SRAM

1) Stand by operation

2) Read operation

3) Write operation

Fig. 1 Standard 6T SRAM

#### **B: STAND BY OPERATION**

A standard one bit 6T SRAM structure is presented in Fig. 1. A one-bit SRAM cell operates in Standby, Read and Write modes. In each mode of operation, the SRAM cell suffers from strong power dissipation. A standard 6T-SRAM cell consists of two cross-coupled inverters- P1, N1, P3, N3, and two pass transistors-N2, N4 to access the data in both the operations. The Write data-enabled line W.L. is pulled to HIGH to turn ON pass transistors N2 and N4 so that it can access the values from the Read access line B.L. and B.L.'.Q and Q' are the stored nodes in Write/Read operation.

**Standby Mode:** In this mode, SRAM will store the value '1' and '0' in Q and Qbars, respectively, so that the pre-charge cycle in SRAM circuitry pulls capacitors HIGH for Bit and Bit bar.' When Write line W.L. will be '1', the access pass transistors are turned ON with a Standby of Read '1' mode for SRAM cell.

**Read Mode**: In this mode, memory should hold some values such that Q=1and Qbar=0 and W.L. should be one, Bit and Bit bar lines should be output lines, the capacitor should be pre-charged, which means voltage should be Vdd near the capacitor point. There is a voltage difference between the  $Q_{bar}$  and the node pt so that the capacitor near the Qbar discharges. Therefore, bit bar voltage decreases, and the output value is one.

Write Mode: In the write operation, memory block holds Q=0 and  $Q_{bar}$ =1, and W.L. should be one, bit and  $bit_{bar}$  are equal to I/P because we have to write into the memory, so we have to make  $bit_{bar}$  grounded.

#### C: MEMRISTOR

Memristor's (memory-resistor) theory was propounded by Leon Chua in 1971 and formalized by Kang [9,10] as a new fundamental circuit element. Memristor consists of a thin nanolayer (6 nm–8 nm) of insulating TiO<sub>2</sub> and a second Oxygen deficient nanolayer of  $TiO_{2-x}$  sandwiched between two Pt nanowires [11,12]. The electrical behavior, as a memory, is determined by the boundary between these two regions. It is based upon the principle where one part of the  $TiO_2$  nanolayer receives oxygen ions (O2-) while the other part of  $TiO_2$  nanolayer loses oxygen ions. A change in the distribution of oxygen ions within  $TiO_2$  nanolayer changes the resistance [13]. The voltage/current relationship of the memristor defined as M(q), can be modeled as:

$$v(t) = \left[R_{on}\frac{w(t)}{D} + R_{off}\left(1 - \frac{w(t)}{D}\right)\right]i(t)$$

.....(1)

where D is  $Ti_{o2/Ti_{o2-x}}$ , film thickness $R_{ON}$  is the resistance for completely doped memristor while  $R_{0ff}$  is the resistance for the undoped region. The width of the doped region w(t) is given as:

for  $R_{ON} \ll R_{off}$  that is the case of the digital circuit; Eq 1 is modified to:

where  $\mu D$  is the average dopant mobility (m2S-1V-1).

#### Low Power Techniques

For VLSI designers, SRAM plays an important role. There are two main reasons; first, it plays a middleman role between the DRAM and CPU as a cache memory, and second, it replaces the DRAM where low power consumption is required.

#### **Power Dissipation**

There are four types of power dissipation

- 1) Dynamic power dissipation

- 2) Switching power dissipation

- 3) Short-circuit power dissipation

- 4) Glitching power dissipation

Here, we are considering peak power and average power dissipation

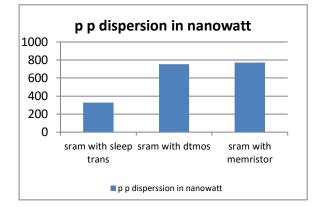

#### **Peak Power Dissipation**

It occurs due to the turning of the power of a laptop or computer. Peak power affects the ckt, supply, and ground line heavily and also impacts other components of the ckt. Due to this, glitches may occur. When read and write operations are held, we may read or write wrong data due to its transient nature. For reducing the amount of power dissipation, we are using different techniques and comparing them with 6T SRAM formed with memristor as explained below:

- 1) SRAM with memristor

- 2) SRAM with sleep transistor technique

- 3) SRAM using DTMOS technique

#### D: 6T SRAM WITH MEMRISTOR

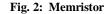

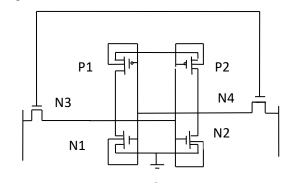

Memristors (also known as memristance) are passive elements with varying resistance [14]. These devices are resistors with varying resistance, which depends on the history of the device. Memristors can be used as a memory where the data is stored as a resistance. For memristive devices, memory is a common application, whereas the additional applications of these memristive devices are functional blocks, such as analog circuits, neuromorphic systems, and logic circuits. The definition of Memristive devices is broader than the definition of the memristor. It is common to use the term memristor for all memristive devices [15,16]. Every change in memresistance depends upon its prior history. The total change takes place through it or the total flux through it.

In this figure, memristors are connected with two NMOS. N1 is cross-connected with the M2 memristor, and N2 is connected with the M1 memristor.

Fig. 3: 6T SRAM with Memristor

## E: SRAM WITH SLEEP TRANSISTOR TECHNIQUE

Fig. 3 shows the SRAM circuit with two sleep transistors, applied on the upside and downside of the circuit. One PMOS transistor and one NMOS transistor are connected in series with the transistors of the cell in such a way so that virtual ground NMOS side and virtual power supply towards PMOS side is formed [17]. The working of the circuit is such that when the circuit is on, the sleep transistor gets activated so that the working of the circuit remains retained, whereas, in OFFstate, the sleep transistor gets OFF so that the source node of the gate floats. Because of this leakage, the path gets cut off. There are two main reasons for power reduction: the low sub-threshold leakage current of high Vthand the other is the stacking of transistors.

Fig. 4: SRAM with Sleep Transistor Technique

### E: 6T SRAM WITH DTMOS TECHNIQUE

Fig. 5 shows the implementation of the SRAM circuit using the DTMOS technique. In DTMOS, dynamic body biasing is used as a substrate, and the gate terminals are connected. Due to this, there is a body effect that changes the threshold voltages of PMOS and NMOS dynamically. If we consider one part of the SRAM using the DTMOS technique, i.e., an inverter, we can see that in the active mode, the logic changes from low to high with a higher speed as the threshold voltage is low for PMOS. In the standby mode, the static leakage current is determined by the sub-threshold current of the NMOS, which has a high threshold voltage. Because of this, the static leakage current decreases considerably [18]. The main advantage of using DTMOS is that it increases cell stability while body biasing improves the tolerance variation in logic.

Fig. 5:Basic 6T SRAM with DTMOS Technique

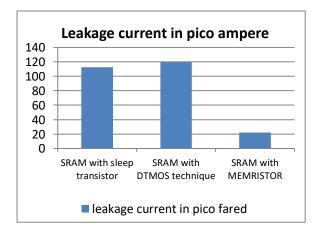

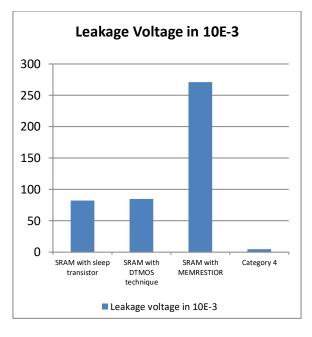

**TABLE -1**

| TECHNIQUE                        | Peak Power<br>Dispersion | Average<br>Leakage<br>Power<br>Dissipation | Leakage<br>Current | Leakage<br>Voltage |

|----------------------------------|--------------------------|--------------------------------------------|--------------------|--------------------|

| SRAM with<br>Sleep<br>Transistor | 329.0E-9                 | 3.084E-9                                   | 112.5E-<br>12      | 82.29E-3           |

| SRAM with<br>DTMOS<br>Technique  | 754.7E-9                 | 83.85E-9                                   | 119.79E-<br>12     | 84.61E-3           |

| SRAM with<br>MEMRESTIOR          | 771.7E-9                 | 15.44E-9                                   | 22.06E-<br>12      | 271.1E-3           |

#### Conclusion

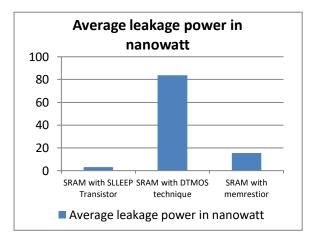

By studying and comparing the simulation results obtained from implementing the SRAM cell usingDTMOS, sleep transistor and 6 T SRAM with memristor, we can infer the following:

1) For the peak power dissipation, we saw that SRAM with sleep transistor gives better results than other techniques applied on 6 T SRAM.

2) From the results, we saw that the average leakage power dissipation is minimum for the sleep transistor technique.

3) Leakage current is minimum for SRAM with memristor.

4)We have also seen that average leakage power is also minimum for the SRAM with the memristor.

#### REFERENCES

- Ambika Prasad Shah, NandakishorYadav, Ankur Beohar, and Santosh Kumar Vishvakarma, "On-chip Adaptive Body Bias for Reducing the impact of NBTI on 6T SRAM Cells", vol. 31.no 2,pp 242-249, 2018

- [2] A. Calimera, M. Loghi, E. Macii, and M. Poncino, "Dynamic Indexing: Leakage-aging co-optimization for caches," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 33, no. 2, pp. 251– 264, 2014.

- [3] M. Wirnshofer, Variation-Aware Adaptive Voltage Scaling for DigitalCMOS Circuits, Springer Series in Advanced Microelectronics, Springer,2013.

- [4] Y. Wang, M. Enachescu, S. D. Cotofana, and L. Fang, "Variationtolerant on-chip degradation sensors for dynamic reliability management systems, Microelectronics Reliability vol. 52, no. 9, pp. 1787–1791, 2012.

- [5] G. D. Panagopoulos and K. Roy, "A three-dimensional physical model for Vth variations considering the combined effect of NBTI and RDF," IEEE Transactions on Electron Devices, vol. 58, no. 8, pp. 2337–2346,

- [6] Paramita Chowdhury, Kuheli Dutta, and Sunipa Roy, A new Gated –Ground- Sleep Architecture for Ultra-Low Leakage of SRAM cell", Emerging Trends in Electronic Devices and Computational Techniques (EDCT)2018, Kolkata

- [7] L. Chang, D.M. Fried, J. Hergenrother, J.W. Sleight, R.H. Dennard, R.K.Montoye, L. Sekaric, S.J. McNab, A.W. Topol, C.D. Adams, K.W.Guarini, and W. Haensch, "Stable

SRAM cell design for the 32 nm node and beyond" Symposium on VLSI Technology, June 2005, pp. 128–129.

- [8] Yiming Li, Shao-Ming Yu, Jiunn-Ren Hwang, and Fu-Liang Yang, "Discrete Dopant Fluctuations in 20-nm/15nm-Gate Planar CMOS", vol55, no 6, June 2008, pp. 1449-1455

- [9] LEON 0. CHUA, "Memristor-The Missing Circuit Element," IEEE Transactions on Circuit Theory, Vol.18, pp. 507–519, September 1971,

- [10] L. Chua and S. M. Kang, "Memristive devices and systems," Proc. IEEE, vol. 64, pp. 209–223, Feb 1976.

- [11] Lin, Yong-Bin Kim, and Fabrizio Lombardi, "Design and Analysis of a 32nm PVT Tolerant CMOS SRAM Cell for Low Leakage and HIGHStability", Elsevier, vol. 43, no. 2, pp. 176–187, 2010

- [12] Shahar Kvatinsky, Guy Satat, Nimrod Wald, Eby G. Friedman, AvinoamKolodny, and Uri C. Weiser, "Memristor-Based Material Implication (IMPLY)Logic: Design Principles and Methodologies," IEEE Transactions On Very Large Scale Integration (VLSI) Systems, VOL. 22, NO. 10, October 2014

- [13] B.H. Calhoun, Yu Cao, Xin Li, Ken Mai, L.T. Pileggi, R.A. Rutenbar, and K.L. Shepard, "Digital circuit design challenges and opportunities in the era of nanoscale CMOS," Proceedings of the IEEE, vol. 96, pp. 343–365, February 2008

- [14] J.P. Kulkarni, K. Kim, and K. Roy, "A 160 mV robust Schmitt trigger based subthreshold SRAM", IEEE Journal of Solid-State Circuits, vol.42, pp.2303–2313, 2007

- [15] B.H. Calhoun, and A.P. Chandrakasan, "A 256 kb 65 nm sub-thresholdSRAM design for ultra-low-voltage operation", IEEE Journal of Solid-State Circuits vol.42, pp. 680–688, 2007

- [16] K. Ragini, Dr. M. Satyam, and Dr. B.C. Jinga, "Variable threshold approach (through dynamic threshold MOSFET)

for the universal logic gate," VLSICS; vol. I, No. I, March 2010.

- [17] L. O. Chua, "Memristor the Missing Circuit Element," IEEE Transactions on Circuit Theory, Vol. 18, No. 5, pp.507-519, 1971

- [18] V. Niranjan andManeesha Gupta, "An Analytical Model of the BulkDTMOS transistor," Journal of Electron Devices; Vol.8; pp. 329-338,2010

- [19] Rakesh Gupta.Article: Design of a Low Voltage Class-AB CMOS Super Buffer Amplifier with Sub Threshold and Leakage Control, International Journal of Engineering Trends and Technology (IJETT), V7(1):13-17; January 2014

- [20] Sourabh Sethi "Memristor Model Based on Generalized Boundary Condition," International Journal of Engineering Trends and Technology (IJETT), V49(4),192-194 July 2017. ISSN:2231-5381

- [21] M. Nizamuudin "Simulation study of CMOS based 6 Transistors SRAM", International Journal of Engineering Trends and Technology (IJETT), V44(5),218-220 February 2017. ISSN:2231-5381

- [22] Garima Upadhyay, Amit Singh Rajput, Nikhil Saxena "A drowsy cache method based 6T SRAM cell with different performance parameter at 32 nm Technology", International Journal of Engineering Trends and Technology (IJETT), V42(8),411-415 December 2016. ISSN:2231-5381

- [23] Pankaj Agarwal, Nikhil Saxena, Nikhita Tripathi. "Low Power Design and Simulation of 7T SRAM Cell using various Circuit Techniques". International Journal of Engineering Trends and Technology (IJETT). V4(5):1688-1693 May 2013. ISSN:2231-5381

- [24] Anitha. K, Darwin.S, Mangala MariSelvi.E, Vijayalakshmi. K" Design and Simulation of SRAM to Reduce Leakage Current using Enhanced Galeor Approach," International Journal of Engineering Trends and Technology (IJETT), V32(7),338-342 February 2016. ISSN:2231-538