#### Review Article

# Advancements in Semiconductor Assembly, Testing, and Packaging: A Global and Regional Perspective

Vy Thi Thanh Huong<sup>1</sup>, Huu Q. Tran<sup>2</sup>

<sup>1</sup>Faculty of Electrical Engineering Technology, Industrial University of Ho Chi Minh City (IUH), The South, Viet Nam. <sup>2</sup>Faculty of Electronics Technology, Industrial University of Ho Chi Minh City (IUH), The South, Viet Nam.

<sup>2</sup>Corresponding Author: tranquyhuu@iuh.edu.vn

Received: 17 May 2025 Revised: 18 June 2025 Accepted: 28 July 2025 Published: 31 July 2025

Abstract - The Assembly, Test, and Packaging (ATP) processes are pivotal in semiconductor manufacturing, ensuring chip reliability and performance for applications from consumer electronics to cutting-edge AI, 6G, and quantum computing systems. This review explores recent ATP advancements, including AI-driven automation, chiplet architectures, Fan-Out Wafer-Level Packaging (FOWLP), and sustainable practices using recyclable materials. It highlights innovative testing methods like adaptive testing and Built-In Self-Test (BIST), alongside emerging trends such as photonic interconnects and advanced thermal management. Key challenges-thermal management, scaling, supply chain resilience, and hardware security-are analyzed, with a special focus on Vietnam's burgeoning role in the global semiconductor ecosystem. By integrating insights from AI-optimized assembly, eco-friendly packaging, and Vietnam's supply chain dynamics, this survey underscores ATP's critical role in nextgeneration electronics and advocates for innovation to address technological and regional challenges.

**Keywords** - Artificial intelligence, Assembly, Test, Packaging, Semiconductor.

#### 1. Introduction

Semiconductor chips are the backbone of modern technology, enabling innovations in smartphones, wearables, automotive systems, aerospace, medical devices, Artificial Intelligence (AI), quantum computing, and neuromorphic systems [1]. While front-end wafer fabrication is essential, back-end Assembly, Test, and Packaging (ATP) processes ensure chip functionality, reliability, and seamless integration through advanced techniques like wire bonding, flip-chip bonding, Through-Silicon Vias (TSVs), wafer-level testing, Built-In Self-Test (BIST), Fan-Out Wafer-Level Packaging (FOWLP), and System-in-Package (SiP) [8, 9]. Driven by the demand for smaller, faster, and energy-efficient devices, ATP innovations-such 2.5D/3Dintegration, as architectures, and heterogeneous integration-are pushing beyond Moore's Law to support AI accelerators, 6G infrastructure, and autonomous vehicles [2]. Specialized ATP solutions, including cryogenic packaging for quantum systems and low-noise interconnects for neuromorphic chips, address unique requirements [10]. Sustainable practices, such as biodegradable polymers and low-temperature bonding, reduce environmental impact [3]. The global semiconductor market, valued at \$595.3 billion in 2021 with a projected 5.6% CAGR through 2030, is propelled by AI, 6G, electric vehicles, and IoT [11]. However, challenges like thermal management, heterogeneous design complexity, vulnerabilities-evident during the 2021-2022 chip shortageand material shortages highlight the need for resilient ATP strategies [12]. Vietnam's National Semiconductor Strategy aims to establish it as a regional electronics hub, bolstered by investments from industry leaders like TSMC [13]. Yet, Vietnam faces hurdles in accessing advanced ATP technologies, skilled labor, and robust infrastructure [6, 7]. This review examines ATP's critical role in next-generation electronics, analyzing global advancements, emerging trends like photonic interconnects and sustainable practices, and Vietnam's opportunities and challenges in the semiconductor ecosystem [3, 4, 13, 14, 50-52].

#### 1.1. Related Works

Prior studies have extensively explored semiconductor ATP technologies, providing a foundation for understanding global advancements. The authors in [1, 2] investigated heterogeneous integration and AI-driven packaging, emphasizing their roles in enhancing chip performance for AI and high-performance computing applications. Recent works, such as [41], have advanced AI-optimized wire bonding, achieving significant yield improvements through real-time defect correction. In [43], the authors analyzed Vietnam's challenges in adopting advanced ATP technologies, highlighting gaps in infrastructure and skilled labor. Similarly, in [48], the authors examined Vietnam's supply chain dynamics, underscoring its growing integration into the global semiconductor ecosystem. Emerging trends-including advanced thermal management and photonic interconnectshave gained attention for addressing high-bandwidth and heat dissipation challenges in next-generation ATP [50, 51]. Despite these contributions, few studies integrate a regional perspective with global technological trends, particularly regarding emerging semiconductor hubs like Vietnam. This review bridges that gap by synthesizing advancements in AIdriven assembly, sustainable packaging, and photonic integration, alongside a focused analysis of Vietnam's opportunities and limitations-offering a novel dual perspective on the evolution of ATP in both global and regional contexts [41, 47, 48, 52].

#### 2. Assembly Process

The assembly process transforms semiconductor dies into functional components, leveraging techniques such as wire bonding, flip-chip bonding, TSVs, and FOWLP [1, 8, 9]. Aldriven automation, utilizing deep learning-based visual recognition, slashes defect rates by 25% in high-volume production, with recent advancements boosting yield by 30% through real-time defect correction [5, 41]. Copper wire bonding, enhanced by palladium-coated wires and optimized parameters, improves reliability by 30% and mitigates oxidation challenges, particularly in Vietnam's high-humidity environments with limited automation [6, 15].

Flip-chip bonding supports high Input/Output (I/O) density, with low-temperature Cu/polymer hybrid bonding reducing energy use by 15–20%. However, Vietnam struggles to achieve sub-3-micron alignment accuracy due to equipment shortages [6, 7, 16, 17]. Fused-silica stitch-chip technology enables cost-effective sub-1-micron alignment for microbump bonding at a 10 µm pitch in RF/mm-Wave multichip modules, offering a viable solution for Vietnam's constrained capabilities [18]. Copper TSVs with low-k dielectrics (e.g., SiCOH,  $k \approx 2.5-3.0$ ) enable 3D stacking, boosting bandwidth by 35-40% and reducing parasitic capacitance by 20-25%, with 0.5–2 microns alignment precision. These advancements lower signal delay to 10–12 ps and thermal stress by 15–20%, enhancing reliability by cutting bonding defect rates to under 5% [10, 19, 20, 42]. Yet, Vietnam's outdated infrastructure limits TSV adoption [6, 7]. FOWLP enhances reliability by 20%, though Vietnam's shortage of skilled engineerscurrently 5,500 against a 2030 target of 50,000-poses challenges [6, 7, 21, 22]. Heterogeneous integration using silicon/glass interposers accelerates integration by 30%, while photonic interconnects achieve 10 Tbps bandwidth, promising significant potential for high-performance systems [2, 23, 50]. Chiplet designs with UCIe standards deliver 1.6 Tbps bandwidth, but Vietnam requires advanced design tools to capitalize on this technology [4, 6]. Sustainable bonding and cryogenic TSVs address environmental and quantum computing needs, with Vietnam's progress tied to global partnerships to overcome equipment and expertise gaps [3, 10, 521.

# 3. Testing Processes

Testing is the cornerstone of semiconductor reliability, ensuring chip performance across applications from consumer electronics to quantum computing [1]. Wafer-level testing employs AI-driven classification with 95% accuracy and Micro-Electro-Mechanical Systems (MEMS) probe cards for sub-5-micron interconnects, though Vietnam faces challenges due to limited access to advanced probe equipment [6, 27, 28]. Burn-in testing simulates early failures, with dynamic systems cutting test time by 25% and eco-friendly chambers reducing energy consumption by 15%. However, high costs hinder adoption by Vietnam's Small and Medium Enterprises (SMEs) [3, 6, 29]. BIST enables on-chip diagnostics, with adaptive BIST improving fault coverage by 20% and AI streamlining design processes, yet Vietnam lacks the expertise to fully leverage this technology [5, 7, 30].

AI-driven testing, utilizing machine learning for defect detection and reinforcement learning for adaptive test pattern generation, achieves 98% defect detection accuracy and reduces test time by up to 40% [31, 44, 39, 49]. Cryogenic testing for quantum chips ensures reliability at low temperatures, but Vietnam's lack of specialized equipment limits its adoption [45]. Emerging trends include AI-optimized testing for 35% cost reduction, sustainable testing with 20% lower carbon emissions, digital twins enabling 50% fewer iterations, and cryogenic methods for quantum systems [3, 10, 32, 33, 44, 45]. To align with global standards, Vietnam requires investment in AI tools, cloud infrastructure, and training, supported by partnerships with industry leaders like Teradyne [6, 34, 53].

# 4. Packaging Technologies

Packaging safeguards semiconductor chips while enhancing performance for applications in AI, 6G, and flexible electronics [1]. System-in-Package (SiP) integrates multiple components, shrinking module size by 30% and leveraging AI for optimized placement, though Vietnam's limited equipment hinders adoption [7, 24, 35]. Advanced materials, such as graphene composites with 2000 W/m·K thermal conductivity, improve cooling, while flexible substrates enable wearables, and sustainable polymers reduce environmental impact. Vietnam, however, faces material supply constraints [3, 6, 36]. Chiplet architectures with UCIe standards deliver 1.6 Tbps bandwidth and 25% efficiency gains via hybrid bonding, but Vietnam lacks advanced design tools [4, 6, 17].

FOWLP boosts reliability by 20%, with AI-driven defect reduction achieving 15% fewer errors and recent advancements in embedded passives and eco-friendly materials enhancing signal integrity by 25% and sustainability by 20% [5, 6, 22, 46, 47]. Advanced thermal management, including microfluidic cooling and phase-change materials, tackles heat fluxes above 100 W/cm², yet Vietnam's access to

these technologies remains limited [14, 51]. 3D packaging with TSVs and hybrid bonding cuts latency by 40%, with glass interposers supporting quantum systems, though Vietnam requires significant R&D investment [7, 19, 25]. Photonic packaging achieves 10 Tbps bandwidth with 50% power reduction, offering transformative potential for Vietnam's consumer electronics sector [40, 50].

Emerging trends-AI-driven design reducing time by 30%, sustainable packaging, cryogenic solutions for quantum systems, and digital twins cutting iterations by 50%-promise enhanced performance and sustainability [3, 10, 13, 24, 33, 56]. Vietnam's packaging ecosystem can advance through global partnerships with firms like TSMC and Amkor, alongside investment in tools and training [6, 13, 48].

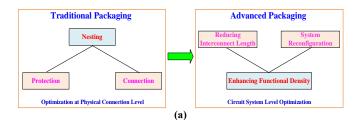

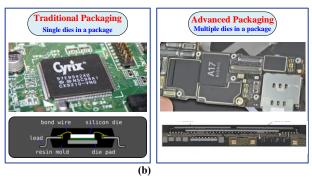

Fig. 1(a, b) Comparison of traditional and advanced packaging functions

Figure 1 illustrates the evolution from traditional to advanced packaging. Traditional packaging focuses on "Nesting" (protection and connection) for physical optimization, while advanced packaging emphasizes "Enhancing Functional Density" (shorter interconnects, system reconfiguration) for circuit-level efficiency, supporting AI, 6G, and quantum applications [2, 4, 19, 35]. The shift highlights 3D stacking, chiplets, and photonic interconnects, with challenges like thermal management and Vietnam's adoption barriers requiring investment [6, 14, 48, 50].

Table 1. Comparison of traditional and advanced packaging technologies

| Aspect         | Traditional Packaging                              | Advanced Packaging                                              |

|----------------|----------------------------------------------------|-----------------------------------------------------------------|

| Structure      | Wire bonding, leadframe-based [1, 9]               | 3D stacking, chiplets, System-in-Package (SiP) [4, 14, 25]      |

| Performance    | Basic I/O density, limited thermal handling [1, 9] | High bandwidth, improved thermal management [4, 10, 14, 19, 51] |

| Applications   | Consumer electronics [1, 6]                        | AI, 6G, HPC, Quantum systems [2, 4, 5, 10, 35, 50]              |

| Scalability    | Limited [9]                                        | High (supports heterogeneous integration) [2, 23, 25]           |

| Adoption in VN | Widely used [6, 7]                                 | Emerging, limited by infrastructure [6, 13, 14, 48]             |

Table 1 presents a comparative overview of traditional and advanced semiconductor packaging technologies across key aspects such as structure, performance, application, scalability, and adoption in Vietnam. Traditional packaging methods, such as wire bonding and leadframe-based designs, offer basic interconnection suitable for consumer electronics but face limitations in performance and integration.

In contrast, advanced packaging incorporates 3D stacking, chiplets, and SiP, enabling higher bandwidth, compact form factors, and support for AI, 6G, and quantum applications. While traditional approaches are widely adopted in Vietnam, advanced technologies are still in the early stages of adoption due to infrastructure constraints.

## 5. Challenges in ATP

ATP faces challenges in thermal management, scaling, supply chains, testing, costs, security, AI integration, and sustainability [1]. Thermal management addresses heat fluxes above 100 W/cm², with microfluidic cooling and phase-change materials reducing temperatures by 30% and 25%, respectively, though Vietnam lacks access to these technologies [5, 7, 14, 51]. Scaling to sub-5-micron pitches increases stress, with low-k dielectrics improving reliability by 20%, but Vietnam's SMEs face equipment costs [6, 20]. Supply chain material shortages delay innovation, with TSMC's expansion aiding Vietnam [6, 12, 13]. Testing heterogeneous systems uses UCIe frameworks (40% test time reduction), but Vietnam lacks infrastructure [4, 7]. Advanced

packaging costs (e.g., \$10M for hybrid bonding) are mitigated by open-source platforms (25% barrier reduction), with Vietnam needing incentives [6, 37]. Hardware security leverages PUFs/AI (30% improvement), but Vietnam lacks cybersecurity expertise [7, 38]. AI integration via federated learning and advanced defect classification improves scalability and accuracy by 20% and 98%, respectively,

though Vietnam needs cloud platforms [6, 39, 51]. Sustainable practices with recyclable materials cut impact by 25%, supported by Vietnam's green policies [3, 6, 55]. Mitigation includes AI, UCIe, sustainable practices, and diversified supply chains, with Vietnam requiring global collaboration [3, 4, 13, 52].

Table 2. Comparison of ATP capabilities - Global vs. Vietnam

| Aspect         | Global Semiconductor Industry                                                     | Vietnam Semiconductor Industry                                    |

|----------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Technology     | Advanced (TSVs, hybrid bonding, UCIe chiplets, photonics) [4, 10, 14, 17, 25, 50] | Limited access to advanced ATP tools [6, 7, 48, 52]               |

| Labor          | Skilled, experienced [2, 3]                                                       | Developing, skill gaps remain [6, 7, 43]                          |

| Investment     | Strong public/private funding [13, 12]                                            | Growing interest, but limited incentives [6, 13, 48, 56]          |

| Infrastructure | Mature R&D and full-stack ATP production [2, 8, 14]                               | Fragmented, reliant on imports or foreign partners [6, 7, 13, 52] |

| Market Role    | Global leaders in innovation (USA, South<br>Korea, Taiwan, Japan) [12, 13]        | Strategic partner, aspiring regional hub [6, 7, 13, 48, 56]       |

Table 2 compares global ATP capabilities with those of Vietnam, highlighting disparities in technology access, skilled labor, infrastructure, and investment. Globally, semiconductor leaders benefit from mature ecosystems with advanced integration technologies, experienced workforces, and substantial investments. In contrast, Vietnam is emerging as a potential hub with growing policy support but faces challenges such as fragmented infrastructure, limited high-end ATP facilities, and dependency on foreign partners. This comparison underscores the need for international collaboration and domestic capacity-building to bridge the capability gap.

# 6. Emerging Trends and Future Directions

ATP is evolving with AI automation, sustainability, quantum/neuromorphic packaging, chiplet standardization, multiscale modeling, photonics, and flexible packaging [1]. AI achieves sub-micron accuracy, cutting test time by 40%, with federated learning and defect classification enhancing scalability and accuracy by 25% and 98%, respectively [5, 7, 31, 50, 51]. Advanced AI algorithms optimize testing and assembly for 6G and quantum systems [53, 57]. Vietnam

needs cloud platforms and training to adopt these technologies [6]. Sustainable manufacturing with biodegradable polymers and eco-friendly FOWLP materials reduces impact by 25%, aligning with Vietnam's green policies [3, 6, 47, 55]. Ouantum/neuromorphic packaging uses cryogenic packages (20% conductivity reduction), but Vietnam needs R&D investment [10, 13, 45]. UCIe chiplet standardization achieves 1.6 Tbps and 30% cost reduction, with Vietnam's SMEs needing tools [4, 6]. Multiscale modeling and digital twins cut prototyping by 50%, but Vietnam lacks computational resources [7, 33]. Silicon photonics delivers 10 Tbps with 50% power reduction, requiring significant investment in Vietnam [6, 40, 50]. Flexible packaging with stretchable interconnects improves durability by 25%, and it has been adopted in Vietnam for consumer electronics [6]. Advanced thermal management and photonic packaging enhance performance for AI and 6G applications, with Vietnam needing global partnerships to access these technologies [51, 54]. Vietnam's SMEs can leverage chiplets/IoE with partnerships, supported by government incentives [13, 48, 56]. Future directions include AI, net-zero processes, quantum/photonic packaging, and UCIe, with Vietnam needing infrastructure, education, and international collaboration [3, 4, 6, 58, 59].

Table 3. Emerging ATP trends in 2023–2024.

| ATP Domain | Key 2023–2024 Trends                               | Expected Impact                                   |

|------------|----------------------------------------------------|---------------------------------------------------|

| Accembit   | AI-guided wire bonding, cryogenic TSVs,            | 20–40% defect reduction, support for quantum      |

|            | photonic interconnects [5, 10, 19, 26, 41, 42, 50] | chips [10, 25, 52]                                |

|            | Reinforcement learning, digital twins, adaptive    | Up to 50% faster, improved yield prediction [31,  |

|            | BIST, AI-driven testing [30-33, 44, 45, 53, 57]    | 32, 34, 57]                                       |

|            | UCIe chiplets, flexible substrates, eco-materials, | Performance boost, sustainability, 3D integration |

| Packaging  | photonic packaging [4, 3, 17, 36, 46, 47, 50, 54]  | [2, 14, 54]                                       |

|            |                                                    |                                                   |

|            |                                                    |                                                   |

Table 3 summarizes the key trends shaping ATP innovation from 2023 to 2024 across three core domains: assembly, testing, and packaging. These include AI-driven wire bonding, cryogenic TSVs for quantum integration, reinforcement learning for adaptive testing, digital twins for faster iteration, and the rise of UCIe chiplets and flexible substrates in packaging. Each trend promises significant improvements in performance, yield, and sustainability, offering both opportunities and challenges for emerging markets like Vietnam. Aligning national strategies with these global trends is essential to remain competitive.

Sustainable manufacturing with biodegradable polymers reduces impact by 25%, aligning with Vietnam's policies [3, 6]. Quantum/neuromorphic packaging uses cryogenic packages (20% conductivity reduction), but Vietnam needs R&D [10, 13].

UCIe chiplet standardization achieves 1.6 Tbps and 30% cost reduction, with Vietnam's SMEs needing tools [4, 6]. Multiscale modeling and digital twins cut prototyping by 50%, but Vietnam lacks computational resources [7, 33]. Silicon photonics delivers 10 Tbps with 50% power reduction, requiring investment in Vietnam [6, 40].

Flexible packaging with stretchable interconnects improves durability by 25%, and it has been adopted in Vietnam for consumer electronics [6]. Vietnam's SMEs can leverage chiplets/IoE with partnerships [13]. Future directions include AI, net-zero processes, quantum/photonic packaging, and UCIe, with Vietnam needing infrastructure and education [3, 4, 6].

#### 7. Conclusion

ATP processes are vital in bridging semiconductor fabrication and system integration, enabling high-performance electronics for AI, 6G, and quantum computing applications [1]. Innovations in hybrid bonding, AI-driven testing, chiplet architectures, and photonic interconnects are transforming the industry, addressing demands for efficiency and scalability [4, 40]. Persistent challenges, including thermal management, hardware security, and sustainability, require ongoing research and innovation [3, 14, 38].

Vietnam's National Semiconductor Strategy positions it as an emerging hub, yet its growth hinges on overcoming infrastructure limitations and skill shortages [6, 13]. To capitalize on global ATP advancements, Vietnam should prioritize investments in AI training programs to build expertise, forge strategic partnerships with industry leaders like TSMC and Amkor, and enhance infrastructure for advanced packaging and testing [6, 13]. By aligning national policies with global trends, Vietnam can strengthen its role in the semiconductor ecosystem. We call for collaborative action-through increased R&D funding, international cooperation, and workforce development-to drive ATP innovation and position Vietnam as a key player in next-generation electronics [4].

## Acknowledgments

Huu Q. Tran and Vy Thi Thanh Huong express gratitude to the Industrial University of Ho Chi Minh (IUH) for providing time and facilities to support this study.

#### References

- [1] John H. Lau, Semiconductor Advanced Packaging, Springer, pp. 1-498, 2021. [CrossRef] [Google Scholar] [Publisher Link]

- [2] Madison Manley et al., "Heterogeneous Integration Technologies for Artificial Intelligence Applications," *IEEE Journal on Exploratory Solid-State Computational Devices and Circuits*, vol. 10, pp. 89-97, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [3] Chien-Hung Kuo et al., "Life Cycle Impact Assessment of Semiconductor Packaging Technologies with Emphasis on Ball Grid Array," *Journal of Cleaner Production*, vol. 276, 2020. [CrossRef] [Google Scholar] [Publisher Link]

- [4] Universal Chiplet Interconnect Express (UCIe) Specification v1.1, Uciexpress, 2024. [Online]. Available: https://www.uciexpress.org/specifications

- [5] Khouloud Limam et al., "Deep Learning-Based Visual Recognition for Inline Defects in Production of Semiconductors," *IEEE Journal of Emerging and Selected Topics in Industrial Electronics*, vol. 5, no. 1, pp. 203-211, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [6] Strategy issued to Develop Vietnam's Semiconductor Industry, Vietnam, 2024. [Online]. Available: https://en.vietnamplus.vn/strategy-issued-to-develop-vietnams-semiconductor-industry-post297035.vnp

- [7] Tran Thi Mong Tuyen, Vietnam's Semiconductor Push Amid the Sino-US Technological Rivalry, 9Dashline, 2024. [Online]. Available: https://www.9dashline.com/article/j36knvtgg322ivilhv3sei0u7d4rzq

- [8] John H. Lau, "Recent Advances and Trends in Advanced Packaging," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 12, no. 2, pp. 228-252, 2022. [CrossRef] [Google Scholar] [Publisher Link]

- [9] SivaChandra Jangam, and Subramanian S. Iyer, "Silicon-Interconnect Fabric for Fine-Pitch (≤10 μm) Heterogeneous Integration," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 11, no. 5, pp. 727-738, 2021. [CrossRef] [Google Scholar] [Publisher Link]

- [10] M. Giustina, "Packaging and Integration Challenges in a Superconducting-Qubit-based Quantum Computer," 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, pp. 14.7.1-14.7.4, 2021. [CrossRef] [Google Scholar] [Publisher Link]

- [11] Global Semiconductor Market Insights, Forecast 2024-2030, Semiconductor Manufacturing & Equipment, 2025. [Online]. Available: https://www.giiresearch.com/report/qyr1635186-global-semiconductor-market-insights-forecast.html

- [12] Navigating the Semiconductor Chip Shortage: A Control-Tower Case Study, McKinsey & Company, 2022. [Online]. Available: https://www.mckinsey.com/capabilities/operations/our-insights/navigating-the-semiconductor-chip-shortage-a-control-tower-case-study

- [13] Annual Report on Form 20-F for 2024, TSMC, 2025. [Online]. Available: https://investor.tsmc.com/english/sec-filings

- [14] Remco van Erp et al., "Co-Designing Electronics with Microfluidics for More Sustainable Cooling," *Nature*, vol. 585, pp. 211-216, 2020. [CrossRef] [Google Scholar] [Publisher Link]

- [15] Hongliang Zhou et al., "Copper Wire Bonding: A Review," *Micromachines*, vol. 14, no. 8, pp. 1-17, 2023. [CrossRef] [Google Scholar] [Publisher Link]

- [16] Chai TC et al., "Fan-Out Wafer Level Packaging Development Line," 2020 IEEE 22<sup>nd</sup> Electronics Packaging Technology Conference (EPTC), Singapore, pp. 440-444, 2020. [CrossRef] [Google Scholar] [Publisher Link]

- [17] Juseong Park et al., "Advanced Cu/Polymer Hybrid Bonding System for Fine-Pitch 3D Stacking Devices," *Advanced Materials Technologies*, vol. 8, no. 20, pp. 1-13, 2023. [CrossRef] [Google Scholar] [Publisher Link]

- [18] Ting Zheng, and Muhannad S. Bakir, "Electrical Demonstration of an RF Embedded Multichip Module Enabled by Fused-Silica Stitch-Chip Technology," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 14, no. 7, pp. 1172-1179, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [19] M.G. Farooq et al., "3D Copper TSV Integration, Testing and Reliability," 2011 International Electron Devices Meeting, Washington, DC, USA, pp. 7.1.1-7.1.4, 2011. [CrossRef] [Google Scholar] [Publisher Link]

- [20] Kuan-Hsun Lu et al., "Thermomechanical Reliability of Through-Silicon Vias in 3D Interconnects," 2011 International Reliability Physics Symposium, Monterey, CA, USA, pp. 3D.1.1-3D.1.7, 2011. [CrossRef] [Google Scholar] [Publisher Link]

- [21] Taewon Yoo et al., "Advanced Chip Last Process Integration for Fan Out WLP," 2022 IEEE 72<sup>nd</sup> Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, pp. 1371-1375, 2022. [CrossRef] [Google Scholar] [Publisher Link]

- [22] Muhammad Hassan Malik et al., "Flexible, Fan-Out, Wafer-Level Packaging Using Polydimethylsiloxane and Printed Redistribution Layers," *Proceedings*, vol. 97, no. 1, pp. 1-3, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [23] Jean-Marc Boucaud et al., "Glass Interposer for Heterogeneous Integration of Flip-Chipped Photonic and Electronic Integrated Circuits," *Applied Physics Letters*, vol. 125, no. 5, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [24] How Chip Makers Are Defying Complexity and Innovating Faster, Synopsys, 2024. [Online]. Available: https://www.synopsys.com/blogs/chip-design/ai-chip-design-dac-2024.html

- [25] Jin Zhao, Fei Qin, and Daquan Yu, "Warpage Prediction and Optimization for Wafer-Level Glass Interposer Packaging," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 14, no. 8, pp. 1394-1402, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [26] Lukas Pfromm et al., "MFIT: Multi-Fidelity Thermal Modeling for 2.5D and 3D Multi-Chiplet Architectures," *arXiv preprint*, pp. 1-26, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [27] Chen He, Hanbin Hu, and Peng Li, "Applications for Machine Learning in Semiconductor Manufacturing and Test (Invited Paper)," 2021 5<sup>th</sup> IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Chengdu, China, pp. 1-3, 2021. [CrossRef] [Google Scholar] [Publisher Link]

- [28] Xuan Luc Le, and Sung-Hoon Choa, "Design of New Au–NiCo MEMS Vertical Probe for Fine-Pitch Wafer-Level Probing," *Crystals*, vol. 11, pp. 1-12, 2021. [CrossRef] [Google Scholar] [Publisher Link]

- [29] Limeng Shi et al., "Investigation on Gate Oxide Reliability under Gate Bias Screening for Commercial SiC Planar and Trench MOSFETs," *Materials Science in Semiconductor Processing*, vol. 174, pp. 1-8, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [30] Partho Bhoumik, Christopher Bailey, and Krishnendu Chakrabarty, "Defect Analysis and Built-In-Self-Test for Chiplet Interconnects in Fan-out Wafer-Level Packaging," 2025 IEEE 43<sup>rd</sup> VLSI Test Symposium (VTS), Tempe, AZ, USA, pp. 1-7, 2025. [CrossRef] [Google Scholar] [Publisher Link]

- [31] Jasmine Edith, "Reinforcement Learning Framework for Adaptive Test Pattern Generation in Logic and Mixed-Signal Ics," *International Journal of Scientific Research in Computer Science and Information Technology*, vol. 3, no. 1, pp. 5-10, 2022. [Publisher Link]

- [32] Muhammad Ali Akbar et al., "Deep Learning-Based Yield Prediction for the Die Bonding Semiconductor Manufacturing Process," Proceedings of the 7th International Conference on Electrical, Control and Computer Engineering, Kuala Lumpur, Malaysia, vol. 2, pp. 75-82, 2023. [CrossRef] [Google Scholar] [Publisher Link]

- [33] Joonick Hwang, and Sang do Noh, "Digital Twin-Based Optimization of Operational Parameters for Cluster Tools in Semiconductor Manufacturing," *IEEE Access*, vol. 12, pp. 122078-122100, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [34] Semiconductor Testing, Teradyne, 2024. [Online]. Available: https://www.teradyne.com/semiconductor-testing

- [35] Haoyu Wang et al., "A Review of System-in-Package Technologies: Application and Reliability of Advanced Packaging," *Micromachines*, vol. 14, no. 6, pp. 1-28, 2023. [CrossRef] [Google Scholar] [Publisher Link]

- [36] Huaqiang Fu et al., "High-Performance Thermal Interface Materials Enabled by Vertical Alignment of Lightweight and Soft Graphene Foams," *Nano Research*, vol. 17, pp. 9293-9299, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [37] Yinxiao Feng, and Kaisheng Ma, "Chiplet Actuary: A Quantitative Cost Model and Multi-Chiplet Architecture Exploration," 59<sup>th</sup> ACM/IEEE Design Automation Conference, San Francisco California, pp. 121-126, 2022. [CrossRef] [Google Scholar] [Publisher Link]

- [38] Md Sami Ul Islam Sami, "Advancing Trustworthiness in System-in-Package: A Novel Root-of-Trust Hardware Security Module for Heterogeneous Integration," *IEEE Access*, pp. 48081-48107, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [39] Erik Jung et al., "Ultra-Broadband Plug-and-Play Photonic Circuit Packaging with Sub-dB Loss," *arXiv preprint*, pp. 1-21, 2025. [CrossRef] [Google Scholar] [Publisher Link]

- [40] Jisu Lim et al., "A Comparative Study on Various Au Wire Rinse Compositions and Their Effects on the Electronic Flame-Off Errors of Wire-Bonding Semiconductor Package," *IEEE Access*, vol. 13, pp. 60317-60326, 2025. [CrossRef] [Google Scholar] [Publisher Link]

- [41] Qianfu Xia et al., "A State-of-the-Art Review of Through-Silicon Vias: Filling Materials, Filling Processes, Performance, and Integration," *Advanced Engineering Materials*, vol. 27, no, 1, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [42] "Emerging Resilience in the Semiconductor Supply Chain," SIA/BCG Report, Semiconductor Industry Association and Boston Consulting Group, 2024. [Google Scholar] [Publisher Link]

- [43] Wenxing Li et al., "SmartATPG: Learning-based Automatic Test Pattern Generation with Graph Convolutional Network and Reinforcement Learning," *Proceedings of the 61<sup>st</sup> ACM/IEEE Design Automation Conference*, San Francisco CA USA, pp. 1-6, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [44] Samuel Neyens et al., "Probing Single Electrons across 300-mm Spin Qubit Wafers," *Nature*, vol. 629, pp. 80-85, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [45] Jiajie Yang, Lixin Xu, and Ke Yang, "Design and Optimization of a Fan-Out Wafer-Level Packaging- Based Integrated Passive Device Structure for FMCW Radar Applications," *Micromachines*, vol. 15, no. 11, pp. 1-15, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [46] Tanja Braun et al., "Fan-Out Wafer and Panel Level Packaging as Packaging Platform for Heterogeneous Integration," *Micromachines*, vol. 10, no. 5, pp. 1-9, 2019. [CrossRef] [Google Scholar] [Publisher Link]

- [47] Vietnam Expands Chip Packaging Footprint as Investors Reduce China Links, Reuters, 2024. [Online]. Available: https://www.reuters.com/technology/vietnam-expands-chip-packaging-footprint-investors-reduce-china-links-2024-11-12

- [48] Tanish Patel et al., "Demystifying Defects: Federated Learning and Explainable AI for Semiconductor Fault Detection," *IEEE Access*, vol. 12, pp. 116987-117007, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [49] Chanki Pandey, and Kalpana G. Bhat, "An Efficient AI-Based Classification of Semiconductor Wafer Defects using an Optimized CNN Model," 2023 IEEE IAS Global Conference on Emerging Technologies (GlobConET), London, United Kingdom, pp. 1-9, 2023. [CrossRef] [Google Scholar] [Publisher Link]

- [50] Huiyu Huang et al., "Photonic Chiplet Interconnection via 3D-Nanoprinted Interposer," *Light Advanced Manufacturing*, vol. 5, no. 4, pp. 542-552, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [51] Huawei Wang et al., "Bioinspired Thermally Conducting Packaging for Heat Management of High Performance Electronic Chips," *Communications Engineering*, vol. 4, pp. 1-9, 2025. [CrossRef] [Google Scholar] [Publisher Link]

- [52] Chia-Nan Wang et al., "Assessing Southeast Asia Countries' Potential in the Semiconductor Supply Chain: An Objectively Weighting Multi-Criteria Decision-Making Approach," *Humanities and Social Sciences Communications*, vol. 11, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [53] Shangding Gu et al., "Few-Shot Test-Time Optimization without Retraining for Semiconductor Recipe Generation and Beyond," *arXiv* preprint, pp. 1-20, 2025. [CrossRef] [Google Scholar] [Publisher Link]

- [54] Becky Lin et al., "Cryogenic Optical Packaging using Photonic Wire Bonds," *APL Photonics*, vol. 8, no. 12, pp. 1-8, 2023. [CrossRef] [Google Scholar] [Publisher Link]

- [55] Chetan Choppali Sudarshan et al., "ECO-CHIP: Estimation of Carbon Footprint of Chiplet-based Architectures for Sustainable VLSI," 2024 IEEE International Symposium on High-Performance Computer Architecture (HPCA), Edinburgh, United Kingdom, pp. 671-685, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [56] Vietnam Offers up to 50 per Cent of Initial Investment Costs for Semiconductor and AI Investors, Vietnam News, 2025. [Online]. Available: https://vietnamnews.vn/economy/1690105/viet-nam-offers-up-to-50-per-cent-of-initial-investment-costs-for-semiconductor-and-ai-investors.html

- [57] S.K. Moore, Machine Learning Might Save Time on Chip Testing, IEEE Spectrum, 2024. [Online]. Available: https://spectrum.ieee.org/semiconductor-testing

- [58] Olga Bubnova, "The Road to Net-Zero Emissions in IC Manufacturing," *Nature Reviews Electrical Engineering*, vol. 1, pp. 214-215, 2024. [CrossRef] [Google Scholar] [Publisher Link]

- [59] Febin Sunny et al., "Silicon Photonic 2.5D Interposer Networks for Overcoming Communication Bottlenecks in Scale-out Machine Learning Hardware Accelerators," 2024 IEEE 42<sup>nd</sup> VLSI Test Symposium (VTS), Tempe, AZ, USA, pp. 1-4, 2024. [CrossRef] [Google Scholar] [Publisher Link]