**Original** Article

# A Physical LDMOST Model and Predictive Simulations for Advanced Technology CAD

Yeonbae Chung

School of Electronic and Electrical Engineering, Kyungpook National University, Daegu, Republic of Korea.

Corresponding Author : ybchung@ee.knu.ac.kr

Received: 06 December 2024

Revised: 05 January 2025

Accepted: 03 February 2025

Published: 22 February 2025

Abstract - This article describes a compact Lateral DMOS Transistor (LDMOST) model incorporated directly into SPICE source code and presents its application to power IC technology CAD. The complete model combines a previously developed semi-numerical static model and a built-in parasitic component model with a charge-based dynamic model. This composite model is based on device physics; thus, it accounts well for important power MOSFET characteristics such as non-uniformly doped channels, reverse-recovery transients and the non-planar drift region. The measurements from the power MOSFET samples support the predictive model, verified in extensive SPICE simulations of several high-voltage circuits. This LDMOST model might be useful in computer-aided optimal design of smart power ICs.

**Keywords -** Charge-based dynamic model, High-voltage MOSFET, Lateral DMOS transistor, Parasitic BJT model, Power IC technology CAD.

# **1. Introduction**

Today, power MOSFETs are extensively used in a variety of high-voltage ICs and power applications like switch-mode power supplies, automotive ICs, power amplifiers, and consumer and telecommunication applications [1]. The optimal design of such high-voltage/power ICs requires SPICE-compatible power MOSFET models, which can predict accurately the static and dynamic performance over a wide operating range.

Power MOSFETs are commonly modeled with subcircuits composed of conventional low-voltage SPICE elements [2-7]. But, the sub-circuit models are inadequate and often suffer from convergence issues. They cannot account properly for the unique device characteristics of high-voltage MOSFETs over a wide range of biases and operating frequencies. While several analytical or physical models for the power MOSFETs have been described in the literature [8-13], an accurate and practical approach for modelling power devices remains elusive yet.

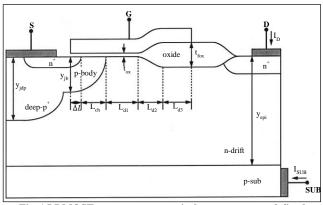

This work develops a compact physical model for Lateral DMOS Transistors (LDMOSTs) and their application to power IC technology CAD. The cross-section of the LDMOST investigated in this study is shown in Figure 1. The p-body is diffused vertically and laterally from the source end, and thus, the device shapes a non-uniformly doped channel region. The poly-silicon gate extended over the thick field oxide forms an accumulation layer in the non-planar drift

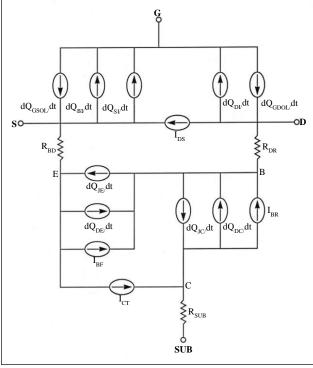

region. Thus, if  $V_{GS}$  exceeds the channel threshold Voltage  $(V_T)$ , electrons can transit from source to drain through the inverted channel. Figure 2 depicts a network representation of the complete LDMOST model. Every DC current and each regional charge in the network are expressed as a function of node voltage differences ( $V_{DS}$ ,  $V_{GS}$ ,  $V_{EB}$ ,  $V_{CB}$ ). The time derivative of each regional charge represents the capacitive transient current. This charge dynamics assures carrier conservation in the simulations. When all network elements in Figure 2 are implemented in SPICE, the complete model will provide the element currents and the partial derivatives of charges and currents needed for the Newton-Raphson iteration in the SPICE program.

The drain-source DC current model for the LDMOST shown in Figure 1 has been addressed in the previous publication [14]. The static model, which is notated with a current source  $I_{DS}$  in Figure 2, is the base of parasitic and dynamic models described in this article; therefore, the symbols and equations in [14] are used in this paper without restatement. The rest of this article is organized as follows. In succession to the  $I_{DS}$  model in [14], Section 2 describes an analytical model for parasitic Bipolar Junction Transistor (BJT) action inherent to this LDMOST structure. Section 3 details the transient behaviours of the device, which are expressed by quasi-static models of the regional charges. Section 4 demonstrates the effectiveness of the complete model through representative power circuit simulations. Finally, the conclusion is provided in Section 5.

Fig. 1 LDMOST structure, geometrical parameters are defined

Fig. 2 A network representing the LDMOST model

## 2. Parasitic BJT Model

In the investigated power MOSFET, there are two p-n junctions (Body-Drift And Substrate-Drift) that form a parasitic p-n-p (Body-Drift-Substrate) BJT. Under normal applications, these built-in junctions are reverse-biased and thus do not influence the circuit operation. However, depending on bias conditions, these two junctions act like a parasitic transistor. For example,  $V_{DS}$  could happen to be negative for a moment during transient switching of the LDMOST in a power IC. If the substrate is tied to the lowest voltage in the high-voltage IC, this negative bias turns on the body-drift junction; thus, the parasitic BJT enters the active mode. If the source and substrate are tied together, the negative value of  $V_{DS}$  activates both junctions; thus, the parasitic BJT operates momentarily in saturation. In either

case, the terminals labelled SUB (substrate), D (drain) and S (source) behave like the collector, base and emitter of the junction transistor. Thereby, the resulting parasitic current might overwhelm the entire device. Here, this parasitic component is modelled with  $I_{CT}$  (base transport current),  $I_{BF}$  (forward base current),  $I_{BR}$  (reverse base current) and 3 ohmic resistances:  $R_{BD}$  (p<sup>+</sup>-body),  $R_{DR}$  (n-drift) and  $R_{SUB}$  (p-substrate).

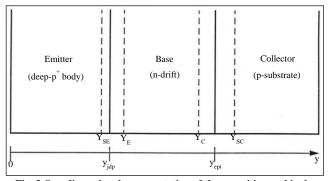

Fig. 3 One-dimensional representation of the parasitic pnp bipolar junction transistor

Figure 3 represents a one-dimensional  $p^+$ -n-p structure for the parasitic BJT, in which  $y_{SC}$ , $y_{C}$ ,  $y_{SE}$  and  $y_E$  denote the boundaries of the Space Charge Region (SCR) at the Collector-Base (C-B) and Emitter-Base (E-B) Junction. With two basic assumptions: 1) wide collector/base/emitter region and 2) high-level carrier injection [15], solving the Ambipolar Transport Equation (ATE) yields the minority mobile hole concentration in the base:

$$p(y) = p_{BF}(y) + p_{BR}(y)$$

(1)

$$p_{BF}(y) = \frac{p(y_E)}{\sinh(W_{BN})} \sinh(\frac{y_C - y}{L_{AB}})$$

(2)

$$p_{BR}(y) = \frac{p(y_C)}{\sinh(W_{BN})} \sinh(\frac{y - y_E}{L_{AB}})$$

(3)

Where  $L_{AB}$  represents the length of ambipolar diffusion at the base and  $W_{BN} (\equiv (y_C - y_E)/L_{AB})$  denotes the normalized base width. The excess hole concentrations at the boundaries are,

$$p(y_E) \cong n_i \left[ \exp\left(\frac{q V_{EB}}{2kT}\right) - 1 \right]$$

(4)

$$p(y_C) \cong n_i \left[ exp\left(\frac{qV_{CB}}{2kT}\right) - 1 \right]$$

(5)

where  $n_i$  represents the intrinsic concentration of electrons, q denotes the magnitude of electronic charge, and kT/q defines the thermal voltage. In addition, the boundaries  $y_E$  and  $y_C$  in the base are characterized as

$$y_E = y_{jdp} + \left[\frac{2\varepsilon_S}{qN_{DD}}(\psi_{bd} - V_{EB})\right]^{1/2} (\text{for } V_{EB} < \psi_{bd})$$

$$= y_{jdp} \qquad (\text{for } V_{EB} \ge \psi_{bd}) \tag{6}$$

$$y_{C} = y_{epi} - \left[\frac{2\varepsilon_{S}N_{AS}}{qN_{DD}(N_{AS}+N_{DD})}(\psi_{sub} - V_{CB})\right]^{1/2}$$

(for  $V_{CB} < \psi_{sub}$ )

$$= y_{epi} \text{ for } V_{CB} \ge \psi_{sub}$$

(7)

Where  $\varepsilon_S$  denotes the silicon permittivity,  $N_{DD}$  and  $N_{AS}$  denote the doping concentrations of base (n-drift) and collector (p-substrate), and  $\psi_{sub}$  (=  $(kT/q)ln(N_{AS}N_{DD}/n_i^2)$ ) and  $\psi_{bd}$  denote the built-in potentials at the C-B and E-B junction.

The BJT base current can be simply characterized as the sum of the back injection component from the base and the recombination component across the base region. For the active mode of the parasitic transistor, the low-level injection is prevalent across the emitter (body) region. Accounting for majority carrier degeneracy and bandgap narrowing [16],

$$I_{BF} = \frac{qA_E}{\tau_{HB}} \int_{y_E}^{y_C} p_{BF}(y) dy + \frac{qA_E n_i^2 y_{jdp}}{N_{AB(eff)} \tau_{nE}} \left[ \exp(\frac{qV_{EB}}{kT}) - 1 \right] (8)$$

Where  $A_E$  denotes the effective area of E-B junction,  $N_{AB(eff)}$  and  $\tau_{nE}$  denote the effective doping concentration and lifetime of the electron in the emitter and  $\tau_{HB}$  denotes the lifetime of the highly injected hole at the base. Whereas, in the reverse mode of the parasitic BJT, the high-level injection is prevalent across the collector (substrate) region. Solving another ATE in the collector yields

$$I_{BR} = \frac{qA_C}{\tau_{HB}} \int_{\gamma_E}^{\gamma_C} p_{BR}(y) dy + \frac{qA_C n_i L_{AC}}{\tau_{HC}} \left[ \exp(\frac{qV_{CB}}{2kT}) - 1 \right] \quad (9)$$

Where  $A_C$  is the effective area of the C-B junction, and  $L_{AC}$  and  $\tau_{HC}$  are the length of ambipolar diffusion and lifetime of highly injected electrons in the collector, respectively.

Now, neglecting carrier recombination in junction SCRs, the model equations characterizing the base transport current can be written as

$$I_{CT} = I_{CF} - I_{CR} \tag{10}$$

$$I_{CF} = A_{EC}J_{TF} - I_{BF} \tag{11}$$

$$I_{CR} = A_{EC}J_{TR} - I_{BR} \tag{12}$$

$$J_{TF} = \frac{1+b_B}{b_B} \left\{ \frac{q n_i^2 y_{jdp}}{N_{AB(eff)} \tau_{nE}} \left[ \exp(\frac{q V_{EB}}{kT}) - 1 \right] - q D_A \frac{d p_{BF}}{dy} |_{y=y_E} \right\}$$

(13)

$$J_{TR} = \frac{1+b_B}{b_B} \left\{ \frac{q n_i L_{AC}}{\tau_{HC}} \left[ \exp(\frac{q V_{CB}}{2kT}) - 1 \right] - q D_A \frac{d p_{BR}}{dy} |_{y=y_C} \right\}$$

(14)

Where  $A_{EC}$  denotes the effective area of BJT crosssection,  $D_A$  is the ambipolar diffusivity in the base, and  $b_B$  defines a ratio of electron-mobility to hole-mobility. In Equations (11)-(14),  $J_{TF}$  and  $J_{TR}$  represent the active-mode emitter current density and reverse-mode collector current density, respectively.

## 3. Charge-Based Dynamic Model

The dynamic behaviors of the LDMOST are modeled with the time derivative of the regional charges within the device. In the network representing the device model, which is shown in Figure 2,  $Q_{DI}$  and  $Q_{SI}$  denote the mobile channel charges related to the drain and source node, and  $Q_{BI}$  denotes the depletion charge in the non-uniformly doped p-body.  $Q_{GDOL}$  and  $Q_{GSOL}$  represent the charges stored at the gate overlap capacitances due to the drift region and the lateral source diffusion, respectively.

$Q_{\rm JC}$  and  $Q_{\rm JE}$  denote the depletion charges at the C-B and E-B junction of the parasitic BJT, and  $Q_{\rm DC}$  and  $Q_{\rm DE}$  denote the injection charges at the forward-biased C-B and E-B junction, respectively. These internal charges are expressed as a function of node voltage differences, and the dynamic properties of the device are represented by the transient current.

$$\frac{dQ_i}{dt} = \sum_j \frac{\delta Q_i}{\delta V_j} \frac{dV_j}{dt}$$

(15)

Where  $Q_i$  is a regional charge, and  $V_j$  is a node voltage difference.

## 3.1. Expressions for $Q_{SI}$ , $Q_{DI}$ and $Q_{BI}$

In the non-uniformly doped channel, the p-body doping concentration is simply approximated as a one-dimensional exponential function:  $N_{AB}(x) = N_{A0}\exp(-\eta_{ch}x/L_{ch})$ , where  $\eta_{ch}(= ln(N_{A0}/N_{DD}))$  defines the doping gradient, and  $N_{A0}$  denotes the maximum concentration at the source. In the linear region, the relationship between the channel potential *V* and the mobile channel charge  $Q_n$  [14, Equation (2)] yields

$$\int_{0}^{x} dQ_{n} = (C_{ox} + C_{D}) \int_{0}^{V(x)} dV$$

(16)

Where  $C_D$  is an average of the p-body depletion capacitance,  $C_{ox} (= \varepsilon_{ox}/t_{ox})$  represents the thin oxide capacitance and  $\varepsilon_{ox}$  denotes the oxide permittivity. Then, substituting  $V(x) \cong (V_{ch}/L_{ch})x$  into Equation (16), in which  $V_{ch}$  is the voltage drop in the channel,

$$Q_n(x) = -\left[C_{ox}(V_{GS} - V_T) + \frac{2C_{D0}\eta_{ch}|\phi_B(0)|}{L_{ch}}x - (C_{ox} + C_{D0})\frac{V_{ch}}{L_{ch}}x\right]$$

(17)

Where,

$$C_{D0} = k_{f3} [q \varepsilon_s N_{A0} / (4 |\phi_B(0)|)]^{1/2}$$

(18)

$$|\phi_B(0)| = (kT/q) \ln[N_{A0}/n_i]$$

(19)

$V_T$  denotes the channel threshold voltage, and  $k_{f3}$  denotes an empirical parameter for depletion capacitance. Following the charge partitioning scheme used in [17],

$$Q_{SI} = W_{z} \int_{0}^{L_{ch}} (1 - \frac{x}{L_{ch}}) Q_{n}(x) dx$$

=  $-\frac{1}{6} W_{z} L_{ch} [3C_{ox}(V_{GS} - V_{T}) + 2C_{D0}\eta_{ch} |\phi_{B}(0)| - (C_{ox} + C_{D0})V_{ch}]$  (20)

$$Q_{DI} = W_{z} \int_{0}^{L_{ch}} \frac{x}{L_{ch}} Q_{n}(x) dx$$

$$= -\frac{1}{6} W_z L_{ch} [3C_{ox}(V_{GS} - V_T) + 4C_{D0}\eta_{ch}|\phi_B(0)| - 2(C_{ox} + C_{D0})V_{ch}]$$

(21)

Where  $W_z$  is the width of the device. Meanwhile, the body depletion charge can be expressed as,

$$Q_{BI} = -W_z \int_0^{L_{ch}} \left[ 2q \varepsilon_S N_{AB}(x) \left( 2|\phi_B(x)| + \frac{V_{ch}}{L_{ch}} x \right) \right]^{1/2} dx \quad (22)$$

Assuming that  $N_{AB}(x)$  and the body Fermi potential  $|\phi_B(x)|$  are approximated as  $\overline{N_{AB}}$  and  $|\overline{\phi_B}|$ , respectively,

$$\log(\overline{N_{AB}}) = (\log N_{A0} + \log N_{DD})/2, \qquad (23)$$

$$\left|\overline{\phi_B}\right| = [|\phi_B(0)| + |\phi_B(L_{ch})|]/2,$$

(24)

The p-body depletion charge in the linear region is written as,

$$Q_{BI} = -W_z L_{ch} K_{BI} \frac{(V_{ch} + 2|\overline{\phi_B}|)^{3/2} - (2|\overline{\phi_B}|)^{3/2}}{V_{ch}}$$

(25)

Where,

$$K_{BI} = \frac{2}{3} \sqrt{2q\varepsilon_S \overline{N_{AB}}}$$

(26)

In the region of the channel current saturation, the mobile and depletion charges related to the channel are obtained from Equations (20), (21) and (25) by replacing  $V_{ch}$  with the onset voltage for the saturation, Equation (10) [14]:

$$V_{ch(sat)} = \frac{c_{ox}(v_{GS} - v_T) + c_{D0}\eta_{ch}|\phi_B(0)|}{c_{ox} + c_{D0}}$$

(27)

In the cutoff region,  $Q_{SI} \cong Q_{DI} \cong 0$ . If  $V_{FBch} < V_{GS} \le V_T$ , where  $V_{FBch}$  represents the flatband voltage in the channel, the depletion charge in the p-body can be written as,

$$Q_{BI} = -\frac{3}{2} W_z L_{ch} K_{BI} \sqrt{2 |\overline{\phi_B}|} \sqrt{\frac{V_{GS} - V_{FBch}}{V_T - V_{FBch}}}$$

(28)

If  $V_{GS} \leq V_{FBch}$ , the channel is accumulated, thus  $Q_{BI} = W_z C_{ox} L_{ch} (V_{FBch} - V_{GS})$ .

## 3.2. Expressions for QGSOL and QGDOL

The overlap capacitance between a heavily doped lateral source diffusion and the gate has a fixed value; thus, the gate overlap charge stored at the parasitic capacitance is simply expressed as  $Q_{GSOL} = (W_z \Delta L \varepsilon_{ox} V_{GS})/t_{ox}$  where  $\Delta L$  is defined in Figure 1, meanwhile, the overlap capacitance between a slightly doped non-planar drift region and the gate varies with the applied bias owing to the depletion of mobile carriers.

When  $V_{DS} < V_{GS} - V_{FBdr}$  in which  $V_{FBdr}$  is an effective flatband voltage at drift region, the gate-to-drain overlap charge is approximated as

$$Q_{GDOL} = -W_{z} [C_{ox} L_{d1} + \frac{(C_{ox} + C_{fox})L_{d2}}{2} + C_{fox} L_{d3}] (V_{DS} - V_{GS} + V_{FBdr})$$

(29)

Where  $C_{fox} (= \varepsilon_{ox}/t_{fox})$  represents the thick oxide capacitance. When  $V_{DS} \ge V_{GS} - V_{FBdr}$ , by using Equations (14)-(16) in [14], the gate-to-drain overlap charge is expressed as,

$$Q_{GDOL} = -q f_{QD} W_z N_{DD} y_{ox} [L_{d1} + \frac{L_{d2}}{t_{fox} - t_{ox}} y_{ox}]$$

(For  $V_{DS} \ge V_{GS} - V_{FBdr}$  and  $y_{ox} \le (t_{fox} - t_{ox})/2$ )

$$= -q f_{QD} W_z N_{DD} [(L_{d1} + L_{d2}/2) y_{ox} + (L_{d2}/2 + L_{d3}) y_{fox}]$$

(For

$$V_{DS} \ge V_{GS} - V_{FBdr}$$

and  $y_{ox} > (t_{fox} - t_{ox})/2$ )(30)

Where  $f_{QD}$  ( $0 < f_{QD} \le 1$ ) represents a depletion charge partitioning parameter, and  $y_{fox}$  and  $y_{ox}$  denote the depletion boundary underneath thick and thin oxide, which are defined in Equations (20) and (21) [14].

#### 3.3. Expressions for $Q_{JE}$ , $Q_{JC}$ , $Q_{DE}$ and $Q_{DC}$

Lastly, the charges associated with the parasitic junction transistor are expressed as follows:

$$Q_{JC} = A_C \sqrt{2q\varepsilon_S \psi_{sub} \frac{N_{DD} N_{AS}}{N_{DD} + N_{AS}} (1 - \frac{V_{CB}}{\psi_{sub}})} (\text{for } V_{CB} < \psi_{sub})$$

= 0 (for  $V_{CB} \ge \psi_{sub}$ ) (32)

$$Q_{DE} = qA_E \int_{y_E}^{y_C} p_{BF}(y) dy + \frac{qA_E n_i^2 y_{jdp}}{N_{AB(eff)}} \left[ \exp(\frac{qV_{EB}}{kT}) - 1 \right]$$

(33)

$$Q_{DC} = qA_C \int_{y_E}^{y_C} p_{BR}(y) dy + qA_C n_i L_{AC} \left[ \exp(\frac{qV_{CB}}{2kT}) - 1 \right]$$

(34)

If the parasitic BJT turns on, the excess mobile charges  $Q_{DE}$  and  $Q_{DC}$  significantly affect the transient characteristics of the device.

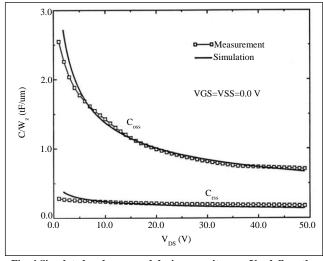

#### 3.4. Model Verification: Coss and Crss

With the test samples fabricated for high-voltage ICs, the dynamic model of the LDMOST has been validated in comparison with experiments.

Figure 4 compares two fundamental device capacitances: output capacitance  $C_{oss} (\equiv \partial Q_{DT} / \partial V_{DS})$  and reverse transfer capacitance  $C_{rss} (\equiv -\partial Q_{GT} / \partial V_{DG})$ , in which  $Q_{DT} (= Q_{DI} - Q_{GDOL} + Q_{JE} - Q_{DE} + Q_{JC} - Q_{DC})$  denotes the total drain charge,  $Q_{GT} (= Q_{GSOL} - Q_{BI} - Q_{SI} - Q_{DI} + Q_{GDOL})$  denotes the total gate charge, and  $V_{DG}$  defines the drain-togate voltage.

As  $V_{DS}$  increases, the magnitude of  $C_{oss}$  decreases rapidly. It can be seen that its correspondence is satisfactory over a wide range of drain-to-source bias voltages. The discrepancy in  $C_{oss}$  is 3.6 % and 2.7 % at  $V_{DS} = 5$  V and 45 V, respectively. Meanwhile, the magnitude of  $C_{rss}$  decreases monotonously with the drain-to-source voltage. A good agreement between model and measurement is observed over an entire range of  $V_{DS}$ .

Fig. 4 Simulated and measured device capacitances,  $V_{\rm SS}$  defines the substrate-to-source voltage

## 4. SPICE Simulations and Discussion

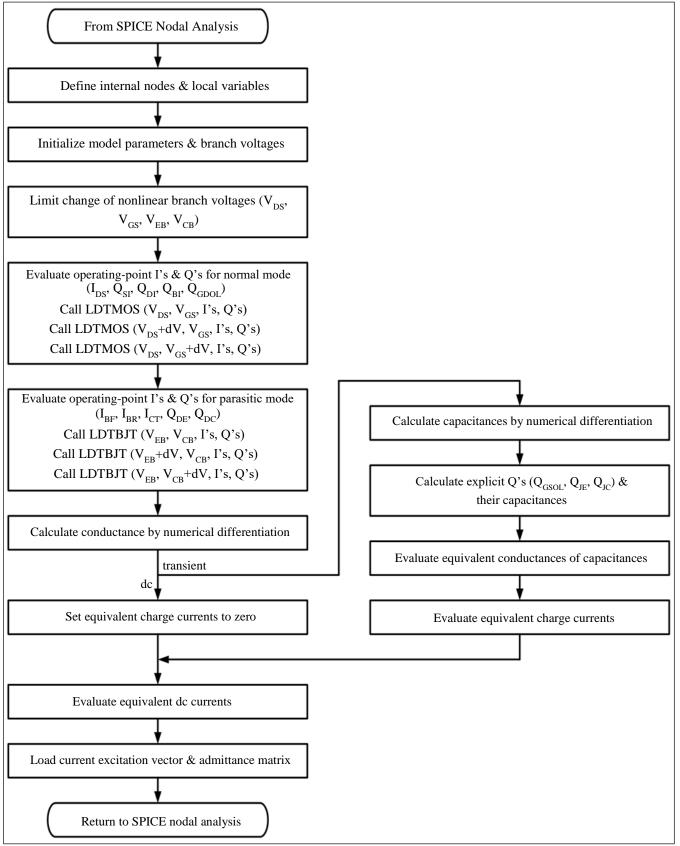

To demonstrate the developed LDMOST model, all network elements in Figure 2 have been incorporated directly into the SPICE2G.6 program [18] by appending three new subroutines (LDMOSFET, LDTMOS and LDTBJT) and altering in part the FORTRAN code of eighteen SPICE subroutines in the software. Basically, the subroutine LDMOSFET shown in Figure 5 links the composite model to the node-voltage analysis in the SPICE program.

The internal resistances  $R_{DR}$ ,  $R_{BD}$  and  $R_{SUB}$  are treated as conductance elements, and the model calculations are performed mostly in the subroutines LDTBJT and LDTMOS. The derivatives of charges and currents necessary for the Newton-Raphson iteration are calculated via multiple calls of LDTBJT and LDTMOS with perturbations of node voltage differences. The subroutine LDTMOS calculates the drainsource current (I<sub>DS</sub>), the intrinsic channel charges (Q<sub>DI</sub>, Q<sub>SI</sub>, Q<sub>BI</sub>) and the gate-to-drain overlap charge (Q<sub>GDL</sub>), and returns their computed values to the subroutine LDMOSFET.

Whereas the subroutine LDTBJT calculates the parasitic BJT currents ( $I_{CT}$ ,  $I_{BR}$ ,  $I_{BP}$ ) and injection charges ( $Q_{DC}$ ,  $Q_{DE}$ ) and returns their computed values to the subroutine LDMOSFET. The other elements ( $Q_{JC}$ ,  $Q_{JE}$ ,  $Q_{GSOL}$ ) are quantified directly in the subroutine LDMOSFET. Accordingly, the three new subroutines in the circuit simulation program calculate the device model equations and link them to the SPICE nodal analysis.

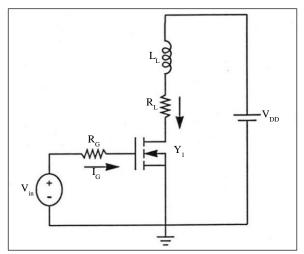

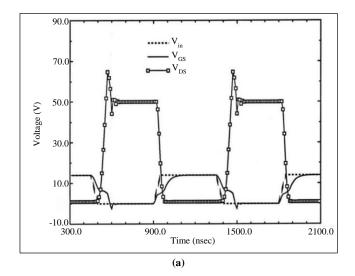

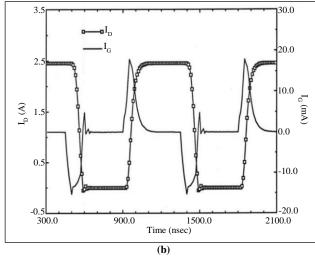

Figure 6 depicts an inductive-resistive load switching circuit using the lateral DMOS transistor, and Figure 7 shows the SPICE-simulated transients for the switching circuit in Figure 6. Note that the element name of the LDMOST device begins with the letter 'Y' in the new version of the SPICE program. The amplitude of the input pulse is 14 V with a rising/falling time of 50 ns. At  $V_{DD} = 50$  V, the load resistance with a value of 20  $\Omega$  results in a switching current of about 2.5 A. All switching transients are well consistent with the theoretical predictions.

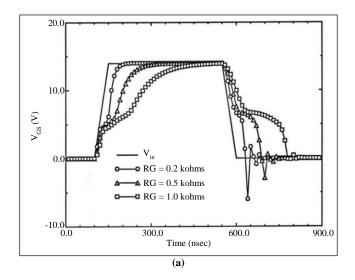

Figure 8 shows the SPICE-simulated gate-drive transients for the switching circuit in Figure 6 with three different values of gate resistance. The gate resistance represented by  $R_G$  ranges from 0.2 to 1.0 k $\Omega$ . The amplitude of the gate pulse is 14 V with a 50 ns rising/falling time. The simulations properly predict the plateau waveforms occurring at the falling and rising edges of the input signal, which are caused by the reverse transfer capacitance in the double-diffused MOS transistor.

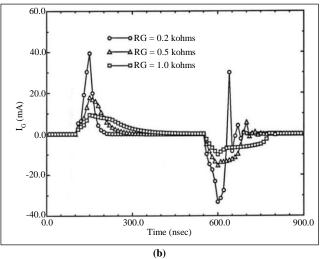

Another simulation result in Figure 9 shows the turn-off transients for the switching circuit in Figure 6 with a small gate resistance of 50  $\Omega$ . The load inductance represented by  $L_L$  ranges from 50 to 180 nH. The amplitude of the gate input is the same at 14 V, and the rising/falling time of the input voltage is also 50 ns. The simulations in Figure 9 adequately describe the overshoots of voltage and current for a given load inductance [19].

Fig. 5 Flowchart of the subroutine LDMOSFET

Fig. 6 Inductive-resistive load LDMOST switching circuit, Wz of  $Y_1$  measures  $5{\times}10^4\,\mu m$

Fig. 7 SPICE-simulated transients for the switching circuit in Figure 6  $(R_G = 0.5 \text{ k}\Omega, R_L = 20 \Omega, L_L = 0.5 \mu\text{H}, V_{DD} = 50 \text{ V})$ : (a) Voltage waveforms, and (b) Current waveforms.

Fig. 8 SPICE-simulated gate-drive transients for the switching circuit in Figure 6 ( $R_L$ = 20  $\Omega$ ,  $L_L$  = 0.5  $\mu$ H,  $V_{DD}$  = 50 V): (a) Gate voltage waveforms, and (b) Gate current waveforms.

Fig. 9 SPICE-simulated inductive switching-off transients for the switching circuit in Figure 6 ( $R_G$  = 50  $\Omega$ ,  $R_L$ = 20  $\Omega$ ,  $V_{DD}$  = 50 V)

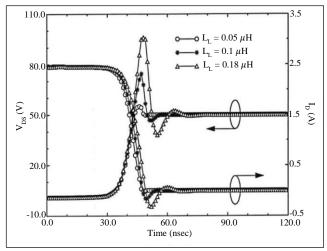

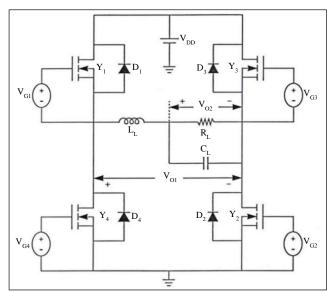

Fig. 10 Full-bridge DC-to-AC converter,  $V_{DD} = 60$  V,  $R_L = 20$   $\Omega$ ,  $C_L = 1$  nF,  $L_L = 0.2 \mu$ H, and the widths of  $Y_1$ ,  $Y_2$ ,  $Y_3$  and  $Y_4$  are all  $5 \times 10^4 \mu$ m

Fig. 11 SPICE-simulated output waveforms for the single-phase DC-to-AC converter in Figure 10

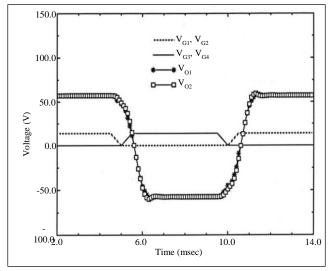

Figure 10 depicts the more complex power circuit, a fullbridge DC-to-AC converter, and Figure 11 shows the SPICEsimulated output waveforms for the conversion in Figure 10. The DC input supply represented by  $V_{DD}$  is 60 V, and the amplitude of the alternate gate pulse signals is 14 V with a rising/falling time of 0.5 ms. In the circuit schematic, D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub> and D<sub>4</sub> represent the inherent p-n (body-drift and substratedrift) junction diodes of the LDMOST, which are utilized frequently to clamp the inductive load switch-off current. Note that the transient simulation in Figure 11 reveals the utility of the parasitic components in the LDMOST circuits.

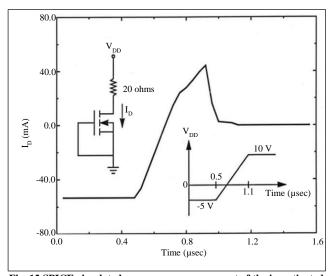

The simulation in Figure 12 shows the reverse-recovery transient for the investigated lateral DMOS transistor. When  $t < 0.5 \ \mu s \ (V_{DS} < 0)$ , in which the parasitic BJT is operating

in saturation, the device stores the injection hole charges in the n-drift region. At  $t = 0.5 \,\mu s$ , a pulse voltage (-5 to +10 V with a 0.6- $\mu$ s rising time) is supplied to the drain terminal via a 20  $\Omega$  resistor to switch the LDMOST to the typical off state. Then, the excess charges in the non-planar drift region begin to diminish by recombination. The SPICE-simulated reverse-recovery current in Figure 12 corresponds well with the theoretical prediction. This feature of the developed model, which cannot be afforded by the behavioral macro models, might be quite useful in the optimal design of smart power ICs.

Fig. 12 SPICE-simulated reverse-recovery current of the investigated lateral DMOS transistor. The device width of the LDMOST measures  $5 \times 10^4$  µm. V<sub>DD</sub> changes -5 to +10 V with a 0.6-µs rising time.

## **5.** Conclusion

In this work, a comprehensive lateral DMOS transistor model, including the inherent BJT model and previous static model, was developed and incorporated directly into the SPICE program. The model has been formulated from quasistatic one-dimensional carrier transport equations, which characterize the regional charges and currents within the device. The capacitive charging/discharging currents are calculated from the regional charges.

The model developed herein accounts for the unique features of power MOSFETs like non-uniformly doped channels, reverse-recovery transients and non-planar drift regions. Moreover, the inter-electrode device capacitances obtained from the charge-based dynamic model exhibit a good agreement with those obtained from the device measurements. A range of SPICE simulations for inductive-load switching circuits, practical DC-to-AC converter and parasitic BJT action indicate that this predictive LDMOST model would be quite effective in TCAD of high-voltage power ICs.

#### Acknowledgments

This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIT) (RS-2023-00242945) and the KEC Corporation. The EDA tool was supported by the IC Design Education Center in Korea.

# Nomenclature

- V<sub>DD</sub> Power supply voltage.

- V<sub>DS</sub> Drain-to-source voltage.

- V<sub>SS</sub> Substrate-to-source voltage.

## References

- V<sub>GS</sub> Gate-to-source voltage.

- V<sub>ch</sub> Voltage drop in channel.

- $V_{EB}$  Emitter-to-base voltage.

- V<sub>CB</sub> Collector-to-base voltage.

- I<sub>D</sub> Drain current.

- $I_G$  Gate current.

- I<sub>SUB</sub> Substrate current.

- I<sub>DS</sub> Drain-source current.

- [1] Bruno Murari, Franco Bertotti, and Guiovanni A. Vignola, *Smart Power ICs: Technologies and Applications*, 1<sup>st</sup> ed., Springer Berlin, Heidelberg, 2002. [Google Scholar] [Publisher Link]

- [2] M.D. Pocha, and R.W. Dutton, "A Computer-Aided Design Model for High-Voltage Double Diffused MOS (DMOS) Transistors," *IEEE Journal of Solid-State Circuits*, vol. 11, no. 5, pp. 718-726, 1976. [CrossRef] [Google Scholar] [Publisher Link]

- [3] H.R. Claessen, and P. Van Der Zee, "An Accurate DC Model for High-Voltage Lateral DMOS Transistors Suited for CACD," *IEEE Transactions on Electron Devices*, vol. 33, no. 12, pp. 1964-1970, 1986. [CrossRef] [Google Scholar] [Publisher Link]

- [4] R.S. Scott, G.A. Franz, and J.L. Johnson, "An Accurate Model for Power DMOSFET's Including Interelectrode Capacitances," *IEEE Transactions on Power Electronics*, vol. 6, no. 2, pp. 192-198, 1991. [CrossRef] [Google Scholar] [Publisher Link]

- [5] M.Y. Hong, and D.A. Antoniadis, "Theoretical Analysis and Modeling of Submicron Channel Length DMOS Transistors," *IEEE Transactions on Electron Devices*, vol. 42, no. 9, pp. 1614-1622, 1995. [CrossRef] [Google Scholar] [Publisher Link]

- [6] A.C.T. Aarts, and W.J. Kloosterman, "Compact Modeling of High-Voltage LDMOS Devices Including Quasi-Saturation," *IEEE Transactions on Electron Devices*, vol. 53, no. 4, pp. 897-902, 2006. [CrossRef] [Google Scholar] [Publisher Link]

- [7] Avinash S. Kashyap et al., "Compact Modeling of LDMOS Transistors for Extreme Environment Analog Circuit Design," *IEEE Transactions on Electron Devices*, vol. 57, no. 6, pp. 1431-1439, 2010. [CrossRef] [Google Scholar] [Publisher Link]

- [8] Y.S. Kim, and J.G. Fossum, "Physical DMOST Modeling for High-Voltage IC CAD," *IEEE Transactions on Electron Devices*, vol. 37, no. 3, pp. 797-803, 1990. [CrossRef] [Google Scholar] [Publisher Link]

- [9] Y.S. Kim, J.G. Fossum, and R.K. Williams, "New Physical Insights and Models for High-Voltage LDMOST IC CAD," *IEEE Transactions on Electron Devices*, vol. 38, no. 7, pp. 1641-1649, 1991. [CrossRef] [Google Scholar] [Publisher Link]

- [10] J. Paredes et al., "A Steady-State VDMOS Transistor Model," *IEEE Transactions on Electron Devices*, vol. 39, no. 3, pp. 712-719, 1992. [CrossRef] [Google Scholar] [Publisher Link]

- [11] J.J. Victory et al., "A Static, Physical VDMOS Model Based on the Charge-Sheet Model," *IEEE Transactions on Electron Devices*, vol. 43, no. 1, pp. 157-164, 1996. [CrossRef] [Google Scholar] [Publisher Link]

- [12] C.W. Tang, and K.Y. Tong, "A Compact Large Signal Model of LDMOS," *Solid-State Electronics*, vol. 46, no. 12, pp. 2111-2115, 2002. [CrossRef] [Google Scholar] [Publisher Link]

- [13] A. Aarts, N. D'Halleweyn, and R. van Langevelde, "A Surface-Potential-Based High-Voltage Compact LDMOS Transistor Model," *IEEE Transactions on Electron Devices*, vol. 52, no. 5, pp. 999-1007, 2005. [CrossRef] [Google Scholar] [Publisher Link]

- [14] Yeonbae Chung, and Taehoon Kim, "A Steady-State LDMOST Model Based on Semi-Numerical Regional Approach," International Journal of Emerging Technology and Advanced Engineering, vol. 12, no. 9, pp. 94-101, 2022. [CrossRef] [Google Scholar] [Publisher Link]

- [15] H.K. Gummel, and H.C. Poon, "An Integral Charge Control Model of Bipolar Transistors," *The Bell System Technical Journal*, vol. 49, no. 5, pp. 827-852, 1970. [CrossRef] [Google Scholar] [Publisher Link]

- [16] J.G. Fossum, and M.A. Shibib, "An Analytic Model for Minority-Carrier Transport in Heavily Doped Regions of Silicon Devices," *IEEE Transactions on Electron Devices*, vol. 28, no. 9, pp. 1018-1025, 1981. [CrossRef] [Google Scholar] [Publisher Link]

- [17] Soo-Young Oh, D.E. Ward, and R.W. Dutton, "Transient Analysis of MOS Transistors," *IEEE Journal of Solid-State Circuits*, vol. 15, no. 4, pp. 636-643, 1980. [CrossRef] [Google Scholar] [Publisher Link]

- [18] Laurence W. Nagel, "SPICE2: A Computer Program to Simulate Semiconductor Circuits," Technical Report No. UCB/ERL M520, Electronics Research Laboratory, University of California, Berkeley, CA, 1975. [Google Scholar] [Publisher Link]

- [19] A.R. Hefner, "An Improved Understanding for the Transient Operation of the Power Insulated Gate Bipolar Transistor (IGBT)," *IEEE Transactions on Power Electronics*, vol. 5, no. 4, pp. 459-468, 1990. [CrossRef] [Google Scholar] [Publisher Link]