# Noise optimization using FIR Filter

Sandeep Kumar G, Nilam Chheda

Sandeep Kumar G PG student/ VLSI and ES, ECE, Ballari institute of technology and management Ballari,

India

Ass. Prof, Nilam Chheda ECE Department, Ballari Institute of Technology and management Ballari, India

#### Abstract

In procedure to make a more reasonable and precise pulse handling framework using ModelSim is created. Simple framework consumes wide room for pulse handling. In this design using ModelSim innovation has supplanted this impediment. It has turned into a to a great degree savvy methods for offstacking computationally escalated advanced signal preparing calculations to enhance general framework execution. The digital-filter execution in Verilog, using the committed equipment assets can viably accomplish application-particular coordinated circuit (ASIC)- like execution while lessening advancement time cost and dangers. A low-pass filter can be actualizing using Verilog HDL. MATLAB device with Verilog framework is most ideal approach to outline computerized framework. In plan of Finite Impulse Response (FIR) channel utilizing adder, coefficients and increase are utilized. Numerous Constant Multiplication (MCM) is the calculation which is utilized as a part of FIR planning to limit multifaceted nature of the circuit, expanded postponement and duplication utilizing huge range. These issues can be improved by utilizing new system known as digit-serial various steady augmentations. It decreases the manysided quality, postponement and area usage.

**Keywords**: *Ripple carry adder, Flip flop, ModelSim, Matlab.*

# I. INTRODUCTION

For quite a while, the near ideal filtering, that is, pulse processing, was just conceivable to perform with analog elements. For instance, established spectrometry speakers with Gaussian pulse forming have been utilized for over 40 years. Because of the improvement of quick simple to advanced converters (ADCs), field programmable Gate-Array (FPGAs), and computerized flag processors (DSPs) amid the most recent couple of decades, it has turned out to be conceivable to digitize beats even after preamplifier or phototube, and handle them in an ongoing. The FPGA can deal with the readout, trigger choices, and easy to medium levels of intricacy of flag processing. Reliant on the information yield and processing prerequisites, the FPGA can be substituted or increased by DSPs for figuring's that are more mind boggling. Thusly, the computerized gadget, which was restricted to the control of the procurement procedure and information stockpiling, has turned out to be plausible for flag preparing too. This quickly opened potential outcomes to configuration instruments with moderately high segment thickness at a sensible cost for every channel. Such instruments could execute numerous simple preparing capacities like pulse segregation, beat abundance sifting, heap up rectification, and pattern rebuilding.

The increase procedure in the advanced framework is extremely well known in designing applications. It is the blend of expansion and moving operation that use more number of machine cycles to actualize little increase because of reiteration of the terms. To conquer these reiteration issues, the MCM strategy is broadly utilized. In any case, such strategy utilized along the mix of various adders. The structure of MCM along different adders does not create idealize answer for power productivity and delay.

# II. BACKGROUND

From the investigation of cases of FIR usage demonstrates that incomplete items in GB calculation prompts best consequences of territory diminishment at gate level.

The moving operation in MCM utilizes D flipflops, as this system takes a shot at bits parallel calculation it is free from equipment. Thus, to share of move, expansion and subtraction operation the abnormal state calculations developed in digit-serial MCM plan. From the Study it presumed that science digit-serial administrators involve less region and are free of the information word length, digit-serial structures offer option low many-sided quality plans when contrasted with bit-parallel designs. For the execution of the idea we utilized the GB technique.

As CSD having 33% diminishment in nonzero components when contrasted with two fold. So to build the viability of code, Sign Digit (SD) was utilized. It helps in DSP to get low power proficient, fast number-crunching structure and decrease zone utilization. In this the numbers get spoken to into set of  $\{1, 0, -1\}$  and they should be as underneath,

1. A couple of non-zeros digits does not show up.

2. Non-zero components must be equivalent to (n+1)/2, where n is digit number.

The Boolean capacity is imperative block of any framework for actualizing the circuit, and it spoken to by the corresponding equation which spoken to by Conjunctive Normal Form (CNF). After this the arithmetical course of action of the bit ought to be finished utilizing the Digital Series Arithmetic (DSA).

In DSA the bits are separated into d-bits and handled serially by applying each block in parallel way. It defeats the detriment of both individual serial and parallel usage. In this paper, deferral and region lessening system is created along these lines DSA strategy is utilized. Along this to accomplish the objective, after as of now predefine techniques are used.

1) Exact Common Sub expression Elimination (CSE) calculation

These calculations can be framed utilizing the means said beneath

- a) Detection of fractional terms

- b) Construction of the Boolean system

- c) Formalization of 0-1 IPL issue

- d) Then decide the base region arrangement

- 2) GB Algorithm

For the execution of FIR with CSA, just consider principle part of the MINAS-DS calculation given beneath,

```

MINAS-DS(T)

\mathbf{R} \leftarrow \{1\}

(R,T) = Synthesize (R,T)

While T \neq \emptyset do

For j = 1 TO 2BW + 1 - 1 Step 2 do

If j \notin R and j \notin T then

Impcostj = ComputeCost ({j},R)

If Impcostj \neq 0 then

A \leftarrow R U \{ j \}

ImpcostT = ComputeTCost (T,R)

Iccost j = impcost j + impcost T

end if

end if

end for

find the intermediate constant, ic, with the minimum

Iccost j cost among all possible constants, j

R \leftarrow R U \{ic\}

(R,T) = synthesize (R,T)

end while

D = synthesizeMinArea(R)

Return D

```

# **III. IMPLEMENTATION**

# A. FIR filter

The transfer-function of FIR is given as (1),

$$H(z) = \frac{Y(z)}{X(z)} = \sum_{n=0}^{N-1} h[n] \cdot z^{-n}$$

(1)

For FIR channel acknowledgment as per equipment and programming recurrence reaction must be in time area arrange. To discover the time space yield test z change was utilized and processed utilizing (2) as underneath.

$$y(n) = \sum_{n=0}^{N-1} h[k] \cdot x[n-k]$$

(2)

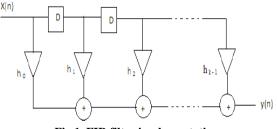

In recipe x [n-k] indicate the specimen input deferred by component n. h [k] is the coefficient of FIR channel and y(n) is channel test yield. As FIR are less delicate than Infinite Impulse Response (IIR) to consistent exactness for same order. FIR is actualized in different acknowledgment groups. Just immediate and improved arrangements were utilized for programming execution reason because of its comfort over different acknowledge. In Digital Signal Processing FIR assumes critical part because of its straight stage trademark alongside bolster forward usage. It comes about into stable channel in advanced world with superior. FIR channel usage is appeared beneath in Fig. 1.

Fig.1. FIR filter implementation

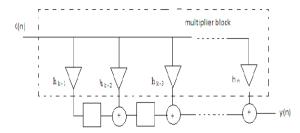

The above design has comparative multifaceted nature in equipment. Henceforth, we go for the execution of transposed frame FIR channel with nonspecific multipliers. The multiplier square of the advanced FIR channel in its transposed Form, where the duplication of channel coefficients with the channel info is acknowledged, has critical effect on the multifaceted nature and execution of the outline in light of the fact that a substantial number of consistent increases are required. So simply gather all increase operation together and name it as multiplier block Fig. 2. This is demonstrated as follows.

Fig.2. Multiplier Block which Takes All Multiplication-Operation Together.

# B. CSA

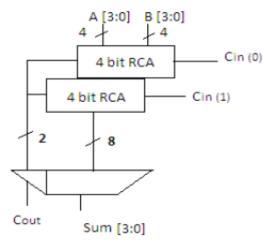

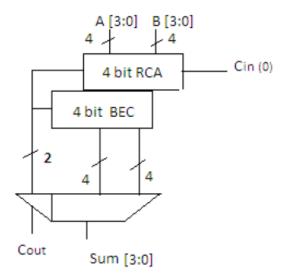

This is utilized for getting more exact outcome than as of now exist strategies. In carry selectadder we utilize two Ripple Carry Adder (RCA) to deliver the yield alongside full adder circuit.

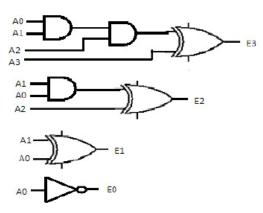

It has complex circuit with high engendering deferral of ripple carry-adder. So as opposed to utilizing two RCA in CSA, blend of one RCA and one Binary to Excess Converter (BEC) is utilized. In any case, to supplant "n bit "RCA "n+1 bit" BEC require. For 4 bit framework taking after Fig. 3 demonstrates the usage of BEC.

Fig.3. BEC execution for 4 bit

To supplant the one RCA circuit with BEC, first need to actualize or rearrange the CSA utilizing two RCA. This execution appear in underneath Fig. 4.

Fig.4. Implementation of CSA with two RCA

In the above circuit to dispense with the detriments of RCA and make the circuit as per detail which are depict in the entire paper. Supplant one RCA with BEC at that point circuit move toward becoming Fig. 5.

Fig.5. Replacement of RCA with BEC

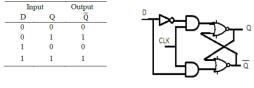

#### C. D-latch

RS flip-flounder functions as essential thing hinders for D flip-flop. It comprise of single I/P (D) driven from S contribution of RS flip-flop and another is D? From R. With this system input mix mistake are lessened. The enabling of second input contribution for D flip-slump which help f/f to hold. This is ANDed with D input. The holding condition happens when empower is 0 bringing about R=0 and S=0 and on the off chance that it is 1 S=D and R =D?. That is yield of framework in these condition equivalents to D. At the point when empower goes to 0, the yield stay in past state.

The working of it shows that it changes just for or rising falling edge of clock. Additionally it stores the information which is invaluable for us for executing the FIR. As it just take every necessary step of passing the yield of BEC and RAC blend to the multiplexer in any case, because of this preferred standpoint of the hook, the postponement of circuit get decreases. The position of this part precisely underneath the BEC can be seen from Fig. 6.

#### D. Full adder and subtractor

These two components are utilized to execute the shifting and adding-operation. As likely the FIRfilter is frame by MCM (Multiple Constant Multiplication) concept [8] [18]. It is the strategy in which, the quantity of factors are lessen and the speed of augmentation moves forward. Likewise it demonstrates the augmentation of set of factors with the specific constants. In FIR channel it distinguishes the regular expansion and subtraction operation and diminishes them to enhance speed of the execution, which lessens the delay in fairly way.

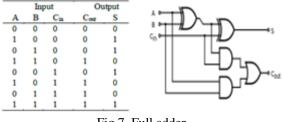

# 1. Full Adder

It is utilized for the addition of binary numbers and creates two yield aggregate and convey. The gate structure is appeared in Fig. 7. It comprises of An and B inputs, Cin is the carry of LSB. S and Cout are the o/p of Sum and Carry separately.

Fig.7. Full adder

To build number of bits (2n) the single piece snake must be place in course to get want yield. Normal portrayal of Carry and Sum alongside connection between them as given in (3).  $Sum=2 \times Cout + S$ (3)

The implementation of full-adder is as (4) and (5),

$$S = A \oplus B \oplus Cin$$

(4)

$$Cout = (A.B) + (Cin.(A \oplus B))$$

(5)

In this execution, the last OR gate before the do o/p might be supplanted by a XOR gate without modifying the subsequent rationale. Utilizing just two sorts of gates is helpful if the circuit is being actualized utilizing straightforward IC chips which contain just a single gate sort for every chip.

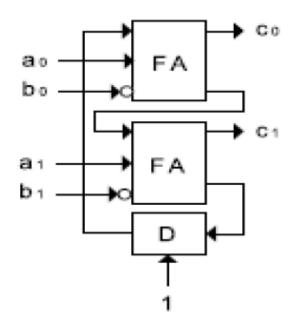

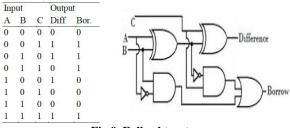

#### 2. Full Subtractor

2's-complement techniques is utilized to actualize subtraction operation (Fig. 8). In which D f/f get instated by 1 along operation of d inverter. The subtraction operation is actualized utilizing 2's

supplement, requiring the introduction of the D fliptumble with 1 and extra d inverter operation. The operation of subtraction is,

Fig.8. Subtraction Operation

The full subtractor is combinational circuit which is utilized to perform subtraction of three bits A, B and C appeared in Fig. 9. It has three data sources, A (minuend) and B (subtrahend) and C (subtrahend) and two o/p D (distinction) and Borrow; D=A-B-C (disregarding the sign tradition)

Acquire = 1 If A < (B+ZC)

The logic circuit and truth table demonstrated as follows,

$$2^{-1}X_3 + 2^{-5}X_1 + 2^{-6}X_7 +

\{2^{-3}X_7 + 2^{-11}X_3\}h[-1]

+ \{2^{-2}X_6 + 2^{-7}X_6\}H[-2]

+ \{2^{-1}X_7 + 2^{-11}X_3\}H[-3]$$

(6)

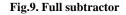

Before giving to CSA condition 6 was plotted (Fig. 10 and Fig. 11). It demonstrates the distinctive blend with least number of moves and includes structure. For execution from above condition consider last estimation of h0 (100011000000)2 and h1

(00100000010)2. At that point change over it into decimal for effortlessness h0 (812)10 and h1 (202)10. It is time and space expending to show increase utilizing GB. Hence taking after case in Fig. 10 and Fig. 11 demonstrates correct technique.

This condition additionally given to CSA which produce last output. The calculation keep running in Xilinx 14.2 shows RTL portray of conclusive calculation with CSA and design.

Fig.11. Simplified Structure of GB Representation

### **IV. RESULT AND DISCUSSION**

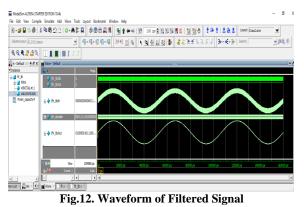

In this paper, essential concentrate is on decrease of Noise, power utilization and delay along lessening in area. In this, the BEC strategy used to improve the expansion and the GB technique that produces extraordinary o/p utilizing less calculation assets. BEC strategy is actualized in Verilog coding and executed utilizing the ModelSim programming. The block diagram includes ripple carry adder, D flipflops and the result will be multiplied with the known factor and finally we get the desired output that is filtered output by removing the noise in the signal which is added by programming using Matlab. Lesser the distortion in the signal higher the signal quality, so this process helps in removing the unwanted distortions in the signal. This process can be furthered improved by different types of adders and filters.

The above screenshot shows the signal which is free from the distortion. Distortion in the signal is filtered using FIR filter which includes ripple carry adder, flip-flop and a multiplication factor which carries a filtering process.

## V. CONCLUSION

The filters are generally utilized as a part of flag preparing and can be executed utilizing programmable advanced processors. Acknowledgment of huge request channels the speed, cost, and adaptability is influenced due to complex calculations and the improvement of FIR channels using different types of adders. This is because of the way that the equipment usage of a great deal of multipliers should be possible on ModelSim which are constrained if there should be an occurrence of programmable advanced processors. This paper predominantly portrays the plan technique for channel which depends on ModelSim, MATLAB and FIR filter. By utilizing these devices time required to get fancied outcomes has turned out to be less. Verilog has been utilized to enter equipment portrayal. To test the accuracy of the outline the watched yield is contrasted and the computed yield comes about because of MATLAB execution that affirms the adequacy of the plan. Verilog codes have been composed, combined, mapped then effectively arranged and prototyped. Channel outlined completely conforms to plan necessities.

#### REFERENCES

- [1] Ray Goslin, Dr. San Jose, CA 95124 "A Guide to Using Field Programmable Gate Arrays (FPGAs) for Application-Specific Digital Signal Processing Performance Gregory Digital Signal Processing" Program Manager Xilinx, Inc. 2100 Logic.

- [2] WANG Jian-xing, YAO Qi-guo. Design of Chebyshev Lowpass Filter Based on MATLAB [J], Journal of Xinxiang University(Natural Science Edition), 2012.2

- [3] Chao Cheng and Keshab K Parhi. Low-Cost Parallel FIR Filter Structures With 2-Stage Parallelism [J].IEEE Transactions on Circuits and Systems I: Regular,2007,54(2):280~290.

- [4] Hu Guang-shu. Digital signal processing-theory, algorithm and realizes[M]. 2nd ed.Beijing: Tsinghua University Press, 2003:296~307.

- [5] Chun Hok Ho, Chi Wai Yu and Leong P. Floating-Point FPGA: Architecture and Modeling IEEE Transactions on Very Large Scale Integration Systems, 2008,17(12): 1709~1718.

- [6] D. E. Borth, I. A. Gerson, J. R. Haug, and C. D. Tho mpson "A flexible adaptive FIR filter VLSI IC". IEEE Journ. Select. Areas Commun. SAC-6(3):494–503

- [7] Lang, "pole radius constraint," IEEE Trans. Signal Processing, vol. 48, Nov. 2011.

- [8] CHEN SH J, GUO J J. Design and implementation of raised cosine roll-off FIR filter based on FPGA[J].Telecom Power Technologies.2007, 24(2):19-21

[9] CHENG X P, QU B, LU G. An application of immune

- [9] CHENG X P, QU B, LU G. An application of immune algorithm in FIR filter design[C].Nanjing: Proceedings of the 2003 International Conference on Neural Networks and Signal Processing,2003(1): 473-475.

- [10] EVEN G, PAUL W J. On the design of IEEE compliant floating point units [J].IEEE Trans on Computers.2000,49(5):398-413.