# Control Allowance of RISC manner Spending Clock Gating Method

G.Jefryferrol, S.Maria Toshak

Students, Electronics & Communication Engineering, Delhi Technological University, Shahbad Daulatpur, Main Bawana Road, Delhi, India

#### Abstract

Control has become an significant feature in enterprise of broad-spectrum determination the mainframes. The conservative these processors consume too much control as associated with other workplaces. This decrease in these processors is done in the manufacture step itself. But this is a composite procedure. If we can appliance the methods for power decrease in obverse end procedure then we can effortlessly design the low control mainframes without any difficulty. In this paper we are suggesting low power enterprise in front end procedure. There is lot of methods to decrease the power. Low regulator feasting helps to decrease the heat dissipation, increase cordless life and upsurge device dependability. This technique is intended using pipelined structure; complete this can strengthening the speed of the procedure. In this we are using 5-stage pipelining. Determined the approach development we comprise numerous low power performances in architectural level also. The highest power reducing technique that has been explored in this development is clock gating. Clock Gating is a well-known method to decrease the power ingesting in this planned Submission Explicit Processor.

**Keywords:** Low power, RISC Processor, Clock gating, Pipelining.

## I. INTRODUCTION

The Intersect Regulator is a device generally originate in computer organizations which deals with interferes produced by the peripherals and the mainframes handle the intersect significances, and governments the implementation to a computer. The overall determination processors deliver one or additional intersect request pins that permit sexteriorstrategies to demand the service deliver by CPU. Consider a case in which processor can handle a great amount of intersects which are originated from exterior strategies. The design necessitates a separate intersect manager which is interfaced to the workspace. More over the mainframe needs around extra- interfacing Circuits

which decreases the performing and propagation the controllingesting of the complete system.

The proposed construction combines the interject regulator and RISC central process unit employs an adaptive timer gating to reduce the complete influence devouring. Power is the one of the enterprise constraint, which is not only functional to portable computers and mobile communication devices but also for high-end systems. Power excess becomes a bottleneck for future technologies. In the early days designers treat the clock signal should not be restricted or disturbed. But clock signal is a major spring for power intemperance and it is an energetic in nature because timer signal is feed into numerous blocks in the processor.

Because all the blocks usage varies within and across a processor, all the blocks not used all the time and gives a chance to reduce the power ingesting of unused blocks. Regulator gating is an efficient technique to reduce the vibrant power intemperance. By ending the clock signal with gated control signal this performance disables the signal to the block when the block is unused. Adaptive technique is one of the techniques used to diminish the dynamic power of the clock. In this technique gating enable signal generated by the block itself depending upon the usage and this technique will reduce the burden on the control unit for generating gating signal.

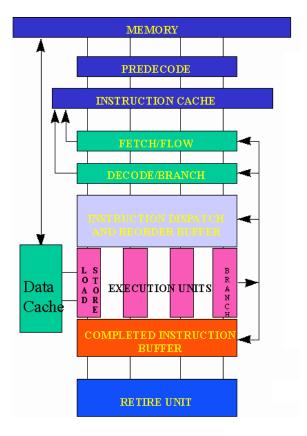

Fig1. RISC Micro Processor

Intersect organization mechanism delivers how interject is controlled by processor. There are numerous methods to reduce the dynamic clock power dissipation. The manager receipts two cycles to procedure the interpose. RISI Controller takes only one cycle for both interject request generation and acknowledgement. The subsequent unit delivers a brief impression of architecture of the RISI SWITCH and clarification about the application and hardware deliberation. Along with a brief explanation about each block current in the architecture is given. Finally a few notes on simulation results.

## II. RISC CLOCK GATING ARCHITECTURE

The power competence is the significant restriction in designing manageable processors, because lower control consequences in lower functioning costs, lower fan noise, and lower cooling necessities.

Therefore, inventers of modern portable systems focus on increased system recital while reducing operating power consumption. Increasing the operating frequency, using more powerful, higher density chips achieves increased system performance, but increasing the performance level intensifications power consumption. Power consumption can be controlled during system operation depending upon the dispensation workload. This approach is called active voltage frequency scaling. According to the CPU workload, there are synchronous between the variation of the operating occurrence and supply voltage.

For the belongings that the assignment is less than the smallest amount voltage necessities to drive the CPU, the permit signal of the clock gating concert will stimulate, through the beginning of the permit signal the controller procedure unit consumes zero power. Hence the lowest energy decrease will obtain The clock gating presentation catalogues low allowancenecessity stages and decreases operating voltage with clock incidence (voltage-frequency scaling), subsequent in condensed average functioning power ingesting. Rendering to the CPU assignments, f and V can be condensed to its small estheights or zero stages established on the software control.

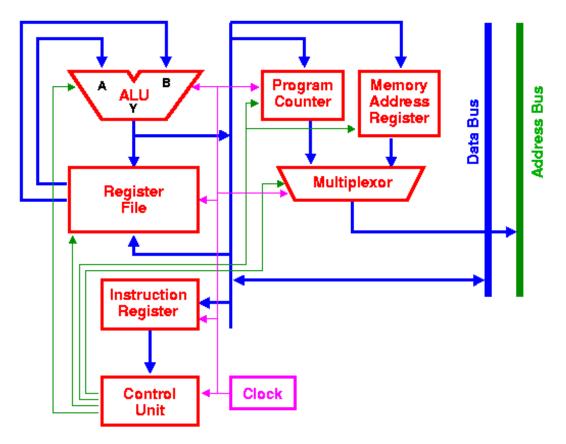

Fig.2. RISC Processor Architecture

## A. Internal Architecture of Risc Controller

The training length of RISC Controller is 16bit wide. This Manager has three flags specifically carry, zero and intersect flags. Both zero and carry decorations are affected only during the performance of arithmetic and logical directives and these are also beneficial for determine the flow of execution when branch and jump instructions take place. CPU checks the interrupt flag after achievement of every instruction to know whether interrupt is available or not.

ALU is capable of execution the Arithmetic and Logical operations (like And, Or, Xor and Cmpl). There are no singular drive registers in the CPU like accumulator and there is no importance between them. An 8-bit statement value providing on the bus together with a READ or WRITE strobe signal designates the retrieved point. This address is either supplied in the program as an absolute value or specified indirectly as the contents of any of the eight registers. There are some specific instructions useful for the controlling of interrupt controller present in the RISC CONTROLLER.

**Fig.3.** Computer Architecture

## **B.** Interrupt Controller:

Present CPU"s deliver one or more intersect application pins that permits external strategies to demand the facility deliver by this component. Interrupt manager are used to growth the amount of disturb inputs accessible to processor. Intersect controller collected with three blocks. They are Interfere Register block, Edge interrupt detection unit and Interrupt request group unit. Intersects are recognized by intersect detection unit through the undesirable clock edge of the clock. Whenever interrupts are noticed, check for the conforming interrupt input masked or not. Exposed interrupt input set the conforming bit in this position register. IRQ group unit produces the interject request by using the IVR insides. Intersect invitation influences the CPU send an acknowledgement signal. Int\_inputs are used to display the intersects approaching from numerous peripherals or external strategies. Each intersect catalogue has an exceptional address and recognized by using Calculator contribution.

To transcribe the fillings of Data input into the interconnect catalogues necessitate a high valid\_wr input. Intrflag input designates the status of this flag current in the CPU.

## III. CLOCK GATING TECHNIQUE FOR LOW POWER RISC PROCESSOR

We evaluate the RISC typical initial. Any IP core (except combinational circuit) can be displayed as an Determinate State Machine which comprises numerous conditions: Idle, Prepared, Run and so on. Correspondingly collection is a state and each arrow shows a transition from a formal to extra. The national and the conversion will be planned to the consecutive circuit and the combinational circuit consistently by parting. When an IP core appearances the work, it arrives the idle national and break there until it agreements additional solicitation from the system bus. We call each of individuals positions excluding IS working state Hence, all states in an IP core are classified to two classes: IS and WS.

When an IP core stays in the IS for particular rotations, it does not need the clock. Consequently, disables the IP clock if the resulting situations are gratified:

1. The present condition of the IP core is IS.

2. There is no entreaty for this IP on the system bus during the modern cycle.

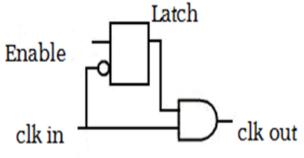

Fig 4 Low Power Gate Clocking

The statuses above also can be articulated as following: If the IP current state is IS and its next state is IS too, the clock is disabled habitually; otherwise, the clock is empowered. We call the circuit realizing the above logic Scout Circuit (SC) which is just a combinational one.

## **IV. FEATURES OF ARCHITECTURE**

- Simple Instructions. The designers of CISC constructions estimated extensive use of complex commands because they close the semantic crack. However, in preparation, it chances out that compilers mostly ignore these directives; the fact has been confirmed by several empirical educations. Because of these explanations, RISC designs use simpler directives. Limited fixed length directions (typically 4 bytes) are provided. No orders association load/store with arithmetic.

- Few Statistics types: CISC ISA sustenance a diversity of data constructions, from simple data types such as numbers and characters to multifaceted archives structures such as records and assemblies. Observed data suggest that complex facts organizations are used relatively infrequently. RISC supports a few simple documents types efficiently and the complex/missing data types are synthesized from them.

- CISC strategies deliver a large number of this method to support multifaceted facts structures as well as to provide flexibility to admittance. However it leads to problems of variable order performance periods& variable-interval instructions. This causes incompetent directive decoding and scheduling.

- RISC enterprises use diffident addressing manners and fixed reserve orders to enable pipelining. Memory -unintended lecture to not deliver.

- Matching Overall Purpose Collections. RISC enterprises permit any record to be recycled in any context, streamlining compiler projects.

- Harvard Structure: Compact order set enterprises often use a this remembrance model, where the instruction torrent and the data stream are theoretically disconnected.

#### A. Benefits of Risc Architecture

- RISC determinations use single a few limitations and these mainframes cannot use the call directions, and consequently, use a stable dimension instruction which is easy to channel.

- This development has a set of instructions, so high-level etymological compilers can harvest more resourceful code.

- It permits in dividuality of using the space on microchips since of its easiness.

- These processors used many catalogs for temporarystimuluses and property the local variables.

- Very less amount of instructional arrangements, a few statistics of orders and a few lecturing modes are required.

- The speed of the procedure can be oppressed and the application time can be reduced.

## B. Drawbacks of Risc Architecture

- Mostly, the concert of the this processors depends on the computer operative or compiler as the data of the compiler plays a energetic role while altering the CISC encryption to a RISC cipher

- While reorganizing the procedure, labeled as a code postponement, will development the size. And, the excellence of this code growth will over depend on the compiler, and also on the mechanism's order set.

- The primary level collection of this computer is also a drawback of the RISC, in which these processors have great recollection supplies on the chip itself. For breast-feeding the instructions, they require very fast memory systems.

#### **V. CONCLUSION**

This computer was intended with high speed and it is realized in low power. We can naturally reduction the power intemperance This design can be used for low power submissions to improve the arrangement generation of the measures. Power can <sup>[13]</sup> be condensed additional by spreading this method at an advanced level of granularity. Thus the design and application of a Processor using Timer method to decrease power intemperance has been talented. The <sup>[14]</sup> benefit of the intended chip is, it can switch an interrupt fast and successfully. It occupies less area and drinks less power. Additional over a mutual CPU in the design achieves the essential processes connected to <sup>[15]</sup> interject supervisor separately from the consistent process. The opportunity for collective the amount of interjects up to data bus width is providing in the enterprise and also protracted to multiprocessor.

#### REFERENCES

- [1] Gated Clock Routing for Low-Power Microprocessor Design, Jaewon Oh and MassoudPedram, Senior Member, IEEE. IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS, VOL. 20, NO. 6, JUNE 2001

- [2] LANG, T., MUSOLL, F, and CORTADELLA, J.: "Individual flip-flops with gated clocks for low power datapaths", IEEE Trans. Circuits S y ~ tI.I, 1997, 44, (6), pp. 507 516

- [3] Xiaotao Chang, Mingming Zhang, Ge Zhang, Zhimni Zhang and Jim Wang, "Adaptive Clock Gating Technique for Low Power IP Core in SoCDesign", IEEE International Symposiumon Circuits And Systems, May (2007), pp. 2120 – 2123, 2007.

- [4] IBM, Multiprocessor Interrupt controller Data Book, March, 2006.

- [5] Kamaraju.M, Lal Kishore.K, Tilak.A.V.N "A Novel Implementation of Application specific Instruction – set processor (ASIP) using verilog" Waste Issue 59,Nov 2011

- [6] Jin Soo Kim Sunwoo, Myung H. Sunwoo, "Three low power ASIP processor designs for communications, video, and audio applications", International Conference on Design & Technology of Integrated Systems in Nanoscale Era, 2007. DTIS, pp. 241-244.

- [7] Y. Takahashi, T. Sekine, and M. Yokoyama, VLSI implementation of a 4\_4-bit multiplier in a two phase drive adiabatic dynamic CMOS logic., IEICE Trans. Electron., vol. E90-C, no. 10, Oct. 2007, in press.

- [8] Qiao Ying-xu, Design of Wireless Sensor Networks Node Based OnTinyOS Operating System. The 3th International Conference on Computer Science and Education[C] 2008.7 1201-1204.

- [9] Jilin Li, "Status and Development Trend of Coal M i n e Safety Monitoring System", Journal, Coal Technology, Harbin, 2008(11), pp. 4-5.

- [10] Wei Chipni, Li Ahaolin, Zheng Qingwei, YeJianfei, and Li Shenglong, "Design of a configurable multichannel interrupt controller", Second Pacific-Asia Conference on Circuits, Communications and System, vol. 1, Aug 2010, pp. 327–330.

- [11] PizhouYe,andChaodong Ling, "A RISC CPU IP core",Second International Conference on Anticounterfeiting,Security and Identification ,August(2008), pp. 356–359,2008.

- [12] H. Jacobson, P. Bose, ZhigangHu, A. Buyuktosunoglu, V.Zyuban, R. Eickemeyer, L. Eisen, J. Griswell, D. Logan, BalaramSinharoy, and J. Tendler, "Stretching the limits of clock-gating efficiency in server-class processors", Eleventh International Symposium on Highperformance Computer Architecture, Feburary (2005), pp . 238-242, 2005.

- 3] Xiaotao Chang, Mingming Zhang, Ge Zhang, Zhimni Zhang and Jim Wang, "Adaptive Clock Gating Technique for Low Power IP Core in SoCDesign", IEEE International Symposium on Circuits And Systems, May (2007), pp. 2120 – 2123, 2007..

- 4] S. Ghosh, D. Mohapatra, G. Karakonstantis and K. Roy, Voltage Scalable High-speed Robust Hybrid Arithmetic Units Using Adaptive Clocking"IEEE Transactions on Very Large Scale Integration Systems, September(2010), Vol. 18, pp.1301-1309, 2010.

- 15] Hai Li, S. Bhunia,Y. Chen,T.N. Vijaykumar and K.Roy," Deterministic clock gating for microprocessor power reduction", Ninth International Symposium on High-Performance Computer Architecture, February (2003), pp. 113 – 122, 2003