# Reduced Power Using Grouping of Flip - Flop Sequential Instruction Pipe Lining

Bhumika Chaurasia1\*, Nishi Pandey2 and Meha Shrivastava3

<sup>#</sup>1PG Student, VLSI Design, Truba Institute of Engineering & Technology, Bhopal 2, 3 Assistant Professor, Truba College of Science and Technology, Bhopal Address Including Country Name

## Abstract (Size 10 & bold &Italic)

The data will be received with the help of clock pulses that reduce the total energy consumption of digital electronic chips [1]-[6]. Driven data is causing area and power overhead that must be considered to minimize the impact of overhead. Therefore, this group is beneficial for FFs whose switching activities are highly correlated and elicit a combined enable signal [7]-[12]. Clock power is the main contributor to dynamic power for the modern design of integrated circuits. Expert work clock synchronization is a surprisingly effective technique for reducing the dynamic competition of sitting outside the rig timing subsystem. This article illustrates the clock activation strategies considered by several testers [13]-[17]. It shows the plane of the encoder and decoder sections of the correspondence structure with a clock arrangement to advance the power without destroying the execution of the function. The extension of the clock activation control required with novel parts of a pair of circuits is less intended by some professionals. A strategy-initiated flip-tumble (PTFF) with adaptive pulse is presented. The work illustrates the properties of PTFF in the rationalization of the control of components and the energy solution, which causes an improved control figure [18]-[24]. Manufacturers minimized HSPICE by light by 51% using an accelerator for channelling the clock loop of the binary clock trace door in the attached file.

**Keywords** — clock synchronization (CG), clock network synthesis, low power design, multi bit flipflop (MBFF), power estimator, DFD and RDFD.

## I. INTRODUCTION

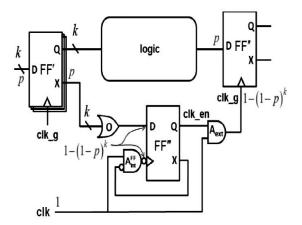

Early Clock Activation (LACG) registers a clock that feeds a signal of one cycle of each FF, depending on the information of the current cycle of the FF on which it is based. For information on forced activation, this additional clock is equipped to exclude most beats. While this is a predominantly favourable position to maintain a strategic distance from AGFF's narrow planning limits and driven by information, to cover a full clock cycle for strong signals and compromise its alligators. Advance for the dissemination of more information driven by the information that requires the learning of vectors that

violate the information of the FF to organize, the LACG is exempt from them. The installation of the LACG logic in usable RTL code is particularly defined and derived from the autonomous hidden logic of the application with purpose. It is easy to use, since it is a significant technique. A technique called data-driven clock activation for flip-flop (FF) was discussed. There, the clock flag that drives the flipflop is placed when the FF position is not subject to change with the clock cycle. When trying to minimize the overload of the activation technique to think, a pair of flip flops is driven by a practically identical clock hail, formed by ORing to connect with the individual flip-flop signals. Activation controlled by information is affected by a short cross window. The total invasion of the XOR, OR, BOLT and AND inputs should not collect the flip-flop configuration time.

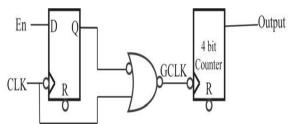

Figure 1: Parallel Bus Specific Clock Gating.

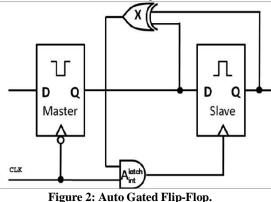

## II. AUTO GATED FLIP-FLOP

Flip-flops have their substance changed to the upper or lower edge of the flag being replaced. In any case, once the rising or falling edge of the Ola changes, the flip-flop substance remains constant, paying little attention to the path along which the data changes. Particularly in standard D flip-flops, correction of the clock signal is transmitted to the D flip-flop, with little attention paid to whether the data is changed or not. The imperative of the clock piece is absorbed by the clock holder to manage the sensed transmission portals. Therefore, if the inverted fight commitment is a photo of its performance, the clock speed will suffocate for direct power.

A technique called data-controlled clock activation for flip-flop (FF) was discussed. When the FF position is not subject to a change in clock cycle, the clock flag that drives the flip-flop is activated. Attempting to minimize the overload of the activation technique for thinking, a pair of flip flops is driven by a practically identical clock hail formed by the O ring, which connects to the signals of the individual flip flops. Information driven by a doorway is affected by a small cross window. The total deletion of the XOR bolt, OR, and AND inputs should not meet the configuration time of the flip flop.

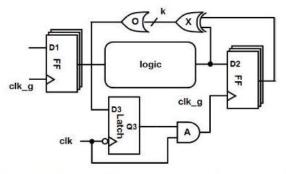

Figure 3: Parallel Bus Specific Clock Gating.

# III. PROPOSED ALGORTHM

The use of force is an important issue in the context of computerized circuits for complex devices with the ultimate goal of portable correspondence and other delivery device. I used the clock activation frame to reduce the use of force. The contour of the clock door reduces the use of force almost (10-19%). Currently, several clock gate frames are used in one day, for example, and a clock gate frame based on NOR and hook. Some processes have been created to reduce the dynamic power, of which the clock speed dominates.

# IV. FLIP FLOP BASED CLOCK GATING

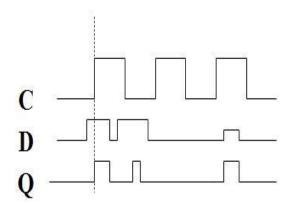

Nor is the snare based on the Nor gated clock layout shown primarily in the picture. Here the corresponding banner is activated through an attached set of direct links with the NOR entry. We can see in the picture that the counter can take one more clock cycle to change its state and then it will usually work until the linear unit is distorted and this point in the same way as another clock cycle. When, its dynamic state is stopped. Figure, we stated that looking at the glitz in the linear unit avoids undesirable yields. In the shape wave, the condition is shown once that the dominant lac is negative and the counter is the one that has a more induced negative edge. The change is rejected as a result of a slight failure due to the retention of the change in the autumn schedule, even though it is an incorrect performance of the counter in the light weight of a one-time outbreak.

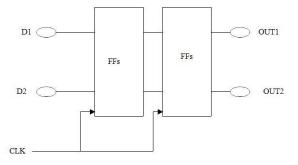

Figure 4: Grouping of Flip Flop

Figure 5: Output of grouping of Flip Flop

Figure 6: Output of negative edge counter when there is some random Hazard at En.

Figure 7: Clock gating of Latch Based NOR gate Circuit.

| q1   |   |        |         |   |       |

|------|---|--------|---------|---|-------|

| Gcik |   |        |         |   |       |

| clk  |   |        |         |   |       |

| en   |   |        |         |   |       |

| q    | 0 | )(1)(2 | )(3 )(4 | 5 | )6 )7 |

Figure 8: Output of negative edge counter when there is some random Hazard at En.

#### V. PROPOSED MODEL

This proposed strategy relies on a collection of FFs that provide a combination of clock times. Multibit D-Hitch flip-flops operate like the head of the hitch, with the exception that the flip flop's performance takes the position of the hitch's FF contribution at this time of a positive edge on the clock lever and it is moved one cycle. The clock is postponed. That is, it is commonly referred to as postponement of postponement. Latch based flipflops can be decrypted as a null request deferred or retention line. The advantage of direct locking on the FF latch on the latch is that the flag on the reflex entry lever is reversed, which is synchronized by the reflex, and the resulting change in latch information will be ignored until the next opportunity. . From the planning table in Figure 1, clearly, the performance cue shifts right to the positive edge. At each positive edge, the performance cue becomes explicitly equal to the same time blocking information and this estimate of the cue is maintained until the next positive edge.

Figure 9: shows that clock time diagram for clock gating

## VI. EXPERIMETAL ANALYSIS

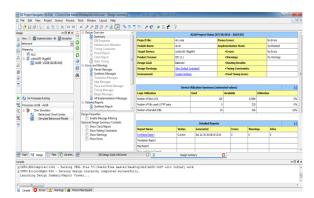

Figure 10: The starting window of project.

Figure 11: The parameter being used in a implementation phase will contain the logic gates.

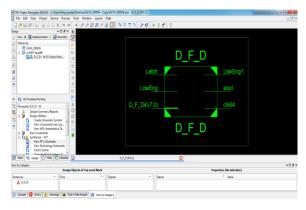

Figure 12: The implementations phase of D\_F\_D with the logic gates and adder.

Figure 13: The all implementation parameter values used in implementation phase with logic utilization value and number of flip flop values.

Figure all initially implementation parameter values for the DFD 2 files used in implementation phase with logic utilization value and number of flip flop values.

| <b>r</b> | Fable | 1: | Data | re | egarding | a | nalysis | , |

|----------|-------|----|------|----|----------|---|---------|---|

|          |       |    |      |    |          |   |         |   |

| Local<br>use           | 6<br>Inputs | Occu-<br>pied<br>file in<br>numb<br>-er | Number<br>of sectors<br>containin<br>g only the<br>correspo<br>nd-ding<br>argument<br>s | Slash<br>with<br>only<br>unreal-<br>ted<br>logic | Quan-<br>tity of<br>bond-<br>ed |

|------------------------|-------------|-----------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------|

| % of<br>DFD            | 17.0        | 31.0                                    | 98.0                                                                                    | 1.0                                              | 14.0                            |

| % of<br>RDFD           | 19.0        | 34.0                                    | 100.0                                                                                   | 3.0                                              | 17.0                            |

| Utilized               | 324.0       | 260.0                                   | 260.0                                                                                   | 0.0                                              | 19.0                            |

| AVAIL<br>ABLE          | 1864.0      | 838.0                                   | 260.0                                                                                   | 260.0                                            | 138.0                           |

| UTILIZ<br>ATION<br>(%) | 21.0        | 33.0                                    | 100.0                                                                                   | 0.0                                              | 16.0                            |

Figure the all implementation parameter values for the DFD 2 files used in implementation phase with logic utilization value and number of flip flop values.

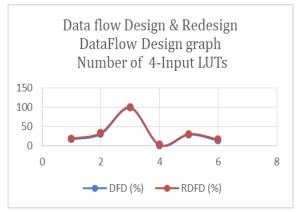

## VII. COMPARATIVE RESULT ANALYSIS

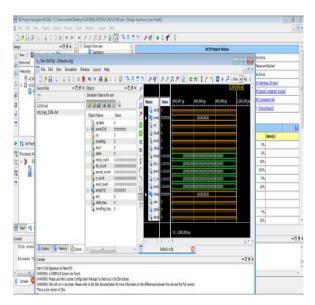

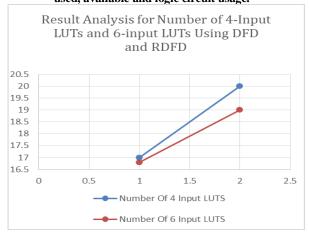

Figure: Analysis of comparative results of Clock Edge Data LUT 4 (1110) for DFD, RDFD,

Figure: Analysis of comparative results of LUT number of 6 inputs and clock edge data (1101) for DFD, RDFD, used, available and logic circuit usage.

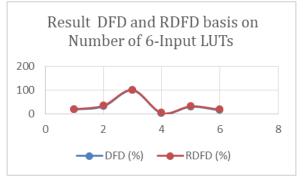

Figure: This shows the analysis of comparative results between DFD and RDFD for the number of 6 inputs in a logic circuit.

## VIII. CONCLUSIONS

Our proposed process minimizes the inconvenience of the planner to examine all flip-flops to meet the prerequisites of planning. The information-driven clock avoids the same planning requirements without account, so that a large part of the planned method that resumes for a single information-driven device decreases the curves. A part of the VLSI default parameters, for example, the default impedance after the clock is turned off, the default duration test is definitely fixed and they are not very diverse. The graphic representation to visualize somersaults depends on the meeting between existing and proposed strategies. The main bar talks about the number of recessions to use the existing system and the second time talks about the flip account to use the proposed strategies.

Currently, VLSI planning is one of the important issues in the field. We talk about different types of flip slap and move enlists to complete the reduced One-piece somersaults and area multi-bit somersaults are realigned to meet the low use of the area. A variety of movement movements are executed with a flip flutter mounted. This proposed strategy is executed in the Xilinx Virtex 5 VLSI family. The interpretive results focus on the number, the postponement and the base of the clock of the use of the flounder. The use of the flip range has been halved. In this sense, this proposed strategy is more appropriate to reduce equipment.

#### REFERENCES

- Shmuelwimer and Israel Koren "Design Flow For Flip-Flop Grouping In Data-Driven Clock Gating", Ieee, 2014, Pp 771-778.

- [2] A. Rangana Yakulu and K. Satya Prasad "Low Power Correlator Using Signal Range And Sub Word Based Clock Gating Scheme", International Journal Of Hybrid Information Technology, 2016, Pp 159-170.

- [3] T.Naresh And M.Lakshmikiran "Power Reduction With Flip Flop Grouping In Data Driven Clock Gating", International Journal Of Engineering And Computer Science, 2015, Pp 11835-11838.

- [4] Dushyant Kumar Soni And Ashishhiradhar "Dynamic Power Reduction Of Synchronous Digital Design By Using Of Efficient Clock Gating Technique", International Journal Of Engineering And Techniques, 2015, Pp 18-23.

- [5] Vidya K And Mr R. Karthik "A Look Ahead Partial Bus Specific Clock Gating Based On Autogated Flipflops", International Journal Of Research In Science And Engineering, 2015, Pp 1-7.

- [6] Saurabhkshirsagar And Dr. M B Mali "Data Driven Clock Gating For Logical Groups In Low Power Applications", Ijesc, 2015, Pp 1454-1457.

- [7] Renukajaiswal, Ranbir Paul And Vikasranjanmahto "Power Reduction In Cmos Technology By Using Tri-State Buffer And Clock Gating", Ijarcet, 2014, Pp 1853-1860.

- [8] R Dhivyabharathi And M Sunil Karthik "A Pass Transistor Based D Flip-Flop Design Using Negative Edge Triggered Circuit", Ijerst, 2015, Pp 63-69.

- [9] S Chindhu And S Thenappan "Pass Transistor Based Conventional Data Flip Flop Design", Ijerst, 2015, Pp 278-284.

- [10] Kakarlasandhya Rani And Krishna Prasad Satamraju "A Novel Approach For Auto Clock Gating Of Flip-Flops", Ijser, 2015, Pp 132-136.

- [11] Anujaaravind And Raseena K.A "Design Of An Alu With A Low Power Lfsr Using Clock Gating", Ijsetr, 2014, Pp 2636-2639.

- [12] Abhishekmashetty, Rajashekar Reddy Merugu, Sanjay Dubey And Vejandla Vijay Bhaskar "Data Driven Clock Gating Technique For Dynamic Power Reduction In Digital Design", Journal Of Chemical And Pharmaceutical Sciences, 2016, Pp 511-514.

- [13] C.Subin Raj, S.Jebasingkirubakaran And P.Balavengateswarlu "Look Ahead Clock Gating Using An Auto Gated Flip Flop For Low Power Application", Journal Of Chemical And Pharmaceutical Sciences, 2016, Pp 969-973.

- [14] D.Nirosha And T.Thangam "Design And Implementation Of 32 Bit Alu Using Look Ahead Clock Gating Logic", Ijeter, 2016, Pp 101-104.

- [15] Shmuelwimer And Aryealbahari "A Look-Ahead Clock Gating Based On Auto-Gated Flip-Flops", Ieee, 2014, Pp 1465-1472.

- [16] Mayuri B. Junghare And Aparna S. Shinde "A Clock Gating Technique Using Auto Gated Flip Flop For Look Ahead Clock Gating", Ijsr, 2013, Pp 1525-1530.

- [17] Zhengxu And Kenneth L. Shepard "Design And Analysis Of Actively-Deskewed Resonant Clock Networks", IEEE, 2009, Pp 558-568.

- [18] Jason H. Anderson And Farid N. "Power Estimation Techniques For Fpgas", Ieee, 2004, Pp 1015-1027.

- [19] D. Popa, Z. Sun, F. Torrisi, T. Hasan, F. Wang And A. C. Ferrari "Sub 200fs Pulse Generation From A Graphene Mode-Locked fiber Laser", Ieee, 2010, Pp 1-3.

- [20] Wimbogaerts, Shankar Kumar Selvaraja, Pieter Dumon, Joostbrouckaert, Katrien De Vos, Dries Van Thourhout And Roelbaets "Silicon-On-Insulator Spectral Filters Fabricated With Cmos Technology", Ieee, 2010, Pp 33-44.

- [21] Shmuel Wimer And Arye Albahari "A Look-Ahead Clock Gating Based On Auto-Gated Flip-Flops", Ieee, 2014, Pp 1465-1475.

- [22] Chaurasia B, Pandey N, Shrivastava M. A Review on Low Power Memory Design Technique. Int J VLSI Signal Process 2019;6:10–3. doi:10.14445/23942584/ijvspv6i3p103.

- [23] Sharma A, Gupta DC. Modified radix 12 Multiplier for reducing area of designed circuit with reduce time delay. Int J VLSI Signal Process 2019;6:6–9. doi:10.14445/23942584/ijvsp-v6i3p102.

- [24] P ARB, J SPM. Design of Programmable High Speed I / O S 2019;6:18–22.