## Original Article

# Design and Verification of Flight Data Acquisition System using UVM

Nainshree Raj<sup>1</sup>, G. Pallavi<sup>1</sup>, M. Poornima<sup>1</sup>, S. Lakshmi<sup>1</sup>, S. Jamuna<sup>2</sup>

<sup>1,2</sup>Department of ECE, Dayananda Sagar College of Engineering, Karnataka, India

Received: 15 April 2023 Revised: 22 May 2023 Accepted: 05 June 2023 Published: 16 June 2023

Abstract - Avionics is an aviation industry platform that provides comprehensive solutions for flight planning, scheduling, and management. Flight data acquisition (FDA) in Avionics refers to the process of collecting and gathering flight-related information from various sources within the Avionics system. It involves integrating data from multiple sources, such as aircraft sensors, air traffic control systems, weather information providers, and airline databases. These diverse sources contribute different types of data, including flight parameters, environmental conditions, and operational details. Overall, flight data acquisition in Avionics plays a crucial role in ensuring the availability of accurate and reliable flight-related information. It enables efficient flight planning, improves operational decision-making, and enhances safety and efficiency in the aviation industry.

**Keywords** - Flight Data Acquisition (FDA), Avionics, FPGA, Universal Verification Methodology (UVM), Electronic Design Automation (EDA).

#### 1. Introduction

Flight data acquisition using Field-Programmable Gate Arrays (FPGAs) and the Universal Verification Methodology (UVM) is an advanced approach to collecting and verifying flight-related data in the aviation industry. FPGAs offer programmable hardware that can be customized to perform specific tasks efficiently, while UVM provides a standardized methodology for verifying digital designs. FPGAs can handle high-speed data processing and offer flexibility in terms of interfacing with various sensors, communication protocols, and data storage units. By leveraging the capabilities of FPGAs, flight data can be acquired, processed, and transmitted in real-time, enabling efficient monitoring and analysis of critical flight parameters.

The UVM verification methodology is employed to ensure the correctness and reliability of the FPGA-based flight data acquisition system. UVM is a standardized verification framework that provides a systematic and scalable approach to verifying digital designs. It involves the creation of reusable verification components, development of test benches, and the application of constrained-random stimulus generation techniques to test the functionality of the design thoroughly. When applied to flight data acquisition using FPGAs, UVM allows for creation of comprehensive test environments that simulate various flight scenarios and sensor inputs. The verification components and testbenches are developed to mimic the realworld flight data acquisition system's behaviour and associated interfaces. Subjecting the FPGA design to a wide range of test scenarios can identify and rectify potential issues or bugs, ensuring the system's robustness and reliability.

## 2. Related Work

The verification process is typically iterative, involving multiple rounds of simulation, formal verification, emulation, and testing until the hardware design is correct and ready for fabrication or development. The complexity of the hardware design and the level of verification required depends on the size, complexity, and criticality of the system being developed.

UVM remains a widely used and supported methodology for hardware verification, providing a standardized and interoperable framework for developing reusable and scalable test benches. Its adoption has significantly improved verification productivity and efficiency, enabling more effective verification of complex designs in the semiconductor industry.

Ning Jia, Hang Chen, and Jun Tian, in the year 2021, proposed a model in "A Design of Configurable Multi-type Flight Data Acquisition System" [1]. The objective of this paper is to compute the acquisition task of multiple types of flight data and store it in real time. The main drawback of this paper is the complexity of the design framework, which

requires a lot of time and effort by professional technicians to operate.

G.V.Jayaramaiah and Chetan Umadi in the year 2020 have published papers on "FPGA implementation of multiprotocol data acquisition system using VHDL" [6]. They have implemented parallel and serial data transfer protocols and all protocols implanted on FPGA kit and modelled using VHDL. Multichannel sensors and different ADC protocols provide digital signals.

Harikrishnan. K, Vishwas. H.N., Vineetha Jain K.V., and Dr. Ramesh Chinthala, in the year 2020, published a paper on "Sensor data acquisition and de-noising using FPGA" [4]. They have designed and implemented an FPGA-based DAQ (Data Acquisition) system. The design shows how a single FPGA fabric can implement an entire system.

## 3. Proposed Work

## 3.1. Flight Data Acquisition Design

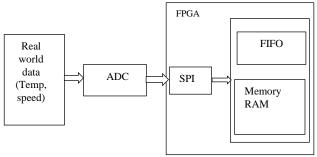

Fig 1. Flight data acquisition system

Flight data acquisition design aims to ensure accurate and reliable data capture, considering factors such as sensor accuracy, sampling rates, synchronization, data integrity, and system redundancy, as shown in the fig1. The collected data is crucial for flight testing, aircraft certification, performance analysis, accident investigations, and ongoing aircraft health monitoring.

The design of a flight data acquisition system involves selecting appropriate sensors to measure the desired parameters, designing the wiring and data buses to transmit the signals, determining the sampling rate and resolution of the data, and specifying the storage capacity and data retrieval methods. The system may utilize data recorders, data acquisition units, signal conditioning modules, and communication interfaces.

The system consists of ADC, interface signal module, FPGA data acquisition module, and memory storage. This system mainly comprises sensors, which collect data from the external world. The configurable aircraft data acquisition system mainly collects engine sensor

parameters, fuselage sensor parameters, atmosphere and other flight data. Analogue to Digital Converter, or ADC, is a data converter that allows digital circuits to interface with the real world by converting an analogue signal into a binary code. To process the analog signal onto digital devices like FPGA, it should be first converted to digital format. After the signal conversion, data is handled using FPGA.

The Serial Peripheral Interface (SPI) is a full-duplex, synchronous, serial data link that is standard across many microprocessors and microcontrollers. It enables communication between microprocessors and peripherals. The SPI protocol is flexible enough to interface with numerous peripherals. Therefore, the main function of the FPGA data acquisition module is to collect many kinds of signals. As the core of the flight data acquisition system, FPGA collects and stores the data. This system is divided into three steps: the signal processing module, the FPGA data acquisition module, and the data storage module.

The signal processing module in a flight data acquisition system is responsible for receiving, conditioning, and processing various sensor signals and data streams from different aircraft systems. It plays a crucial role in converting analog signals into digital format, applying necessary filters and transformations, and preparing the data for storage or transmission.

The data acquisition module interfaces with a wide range of sensors and data sources throughout the aircraft. These may include airspeed sensors, altimeters, gyroscopes, accelerometers, engine parameters, control surfaces, avionics systems, and more. The signals from these sources are acquired and converted into digital form for further processing.

The FDR (Flight Data Recorder), commonly known as the "black box," is a specialized device installed on aircraft to record various parameters and flight information. It captures data such as altitude, airspeed, vertical acceleration, heading, control inputs, engine parameters, and more. The FDR typically uses solid-state memory or magnetic tape to store data, and it is designed to withstand extreme conditions, including crashes and fires, to ensure data survivability. Flight data acquisition systems are crucial for flight safety and performance monitoring. The collected data can be analyzed to identify trends, anomalies, and potential issues, enabling proactive maintenance and incident investigation.

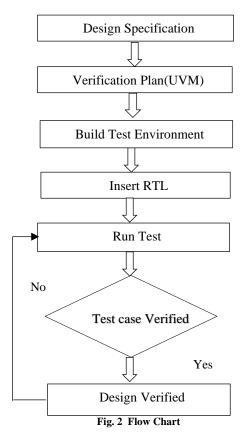

## 3.2. Verification Plan

A verification plan is done before verifying any project to ease the work of the verification engineer. Based on the requirement, a verification plan is to be built, including a list of test cases and coverage models. A verification plan defines what needs to be verified in a hardware design and then drives the verification strategy.

## 3.3. Universal Verification Methodology

Universal Verification Methodology (UVM) is a standardized methodology for the functional verification of digital designs or systems. It provides a framework and set of guidelines for creating modular and reusable testbenches and verification components. UVM is widely adopted in the semiconductor industry and is supported by various electronic design automation (EDA) tools.

In the Universal Verification Methodology (UVM), several key components work together to create a modular and reusable testbench environment. These components include:

## 3.3.1. Testbench Top

This is the main component of the testbench hierarchy. It coordinates the overall verification process and instantiates other testbench components.

## 3.3.2. Testbench Configuration

The testbench configuration specifies the desired configuration parameters for the testbench, such as clock frequency, interface configurations, or specific feature enablement.

Fig. 3 UVM Architecture

## 3.3.3. DUT (Design Under Test) Agent

The DUT agent is responsible for interfacing with the design and translating the testbench transactions to the DUT's signals or interfaces. It contains the necessary drivers, monitors, and sequences for communication with the DUT.

#### 3.3.4. Test

The test component defines a specific test scenario or use case that needs to be verified. It encapsulates the test sequence and may contain test-specific data and configuration information. The test component typically inherits from the uvm\_test base class.

#### 3.3.5. Environment

The environment component acts as the top-level container for the testbench. It provides the infrastructure for coordinating and controlling the verification process. The environment instantiates and connects other components, such as agents, monitors, drivers, and scoreboards. It usually inherits from the uvm\_env base class.

## 3.3.6. Agent

An agent represents a specific interface or protocol within the design under test (DUT). It consists of multiple sub-components, each with a specific role:

#### Sequencer

The sequencer generates sequences of transactions or stimuli to be applied to the DUT. It controls the flow and timing of the transactions and manages sequence dependencies.

#### Driver

The driver receives the transactions from the sequencer and drives the stimuli onto the DUT's interface signals. It converts the transaction-level protocol into the signal-level protocol.

#### Monitor

The monitor component observes the DUT's interface signals, captures transaction-level information and converts it into transactions for analysis and checking in the testbench.

#### Scoreboard

The scoreboard compares the expected results, generated by the test or reference model, with the actual results obtained from the DUT. It checks for functional correctness and reports any discrepancies.

## Sequences

Sequences represent a sequence of transactions or stimuli that are applied to the DUT. Sequences are typically generated by the sequencer and control the specific test scenario.

## Sequence Items

Sequence items are the individual transactions or stimuli that make up a sequence. They encapsulate the data and control information to be applied to the DUT.

## Configuration

The configuration component manages the configuration settings for the testbench and DUT. It provides a centralized location for storing and accessing configuration information.

#### Coverage

The coverage component tracks which parts of the design have been exercised by the testbench. It collects coverage data and generates coverage analysis reports, helping to ensure that the verification process is thorough.

#### Assertions

Assertions are used to define specific properties or conditions that the DUT must satisfy. They help capture and verify design properties and can be used for design and testbench verification.

These components work together to create a comprehensive UVM testbench environment for verifying digital designs. They provide a modular and scalable infrastructure that promotes reusability, maintainability, and efficient verification of the design under test.

## 4. Results

Flight Data Acquisition System is designed in which random inputs are given and stored in memory. The design includes SPI protocol as Interface and FIFO to store data in the memory. The design acts as DUT (Design under test), verified using UVM (Universal Verification Methodology). Each block of the UVM is designed, which includes: UVM

Interface, Sequence, Sequence Item, Sequencer, Driver, Monitor, Agent, Scoreboard, Environment, and Test.

Here are the simulation results of the flight data acquisition system, which is verified using UVM.

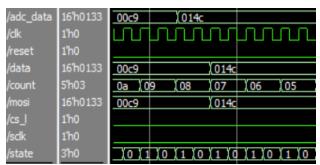

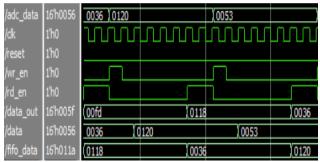

Fig. 4 SPI Interface

The data from the sensor is interfaced with FPGA using SPI interface, and obtained results are shown in fig4.

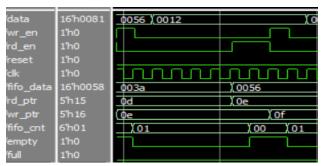

Fig. 5 FIFO

Fig. 6 Verification using UVM

The flight data acquisition system is verified using UVM testbench and observed waveform is shown above in fig. 6.

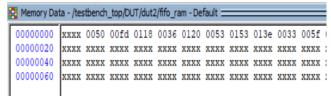

Fig. 7 Memory Block

The data processed using FPGA is stored in a memory block; the above fig shows the data stored in memory during simulation.

```

@ 335: uvm_test_top.env.scb [SCOREBOARD] -----:RESULT:: -----

@ 335: uvm_test_top.env.scb [] adc_data:118

@ 335: uvm_test_top.env.scb [] data_out:fd

@ 335: uvm_test_top.env.scb [SCOREBOARD] TEST PASSED

Got Transaction adc data=53

```

Fig. 8 Log report when the test is passed

When the test case is verified, it prints as a test passed in the transcript window, which is shown in Fig 8.

```

@ 175: uvm_test_top.env.scb [SCOREBOARD] -----::RESULT::

@ 175: uvm_test_top.env.scb [] adc_data:50

@ 175: uvm_test_top.env.scb [] data_out:0

@ 175: uvm_test_top.env.scb [SCOREBOARD] TEST FAILED

```

Fig. 9 Log file output when the test is failed

When the test case is not verified, it prints as the test failed in the transcript window, which is shown in Fig 9.

#### 5. Conclusion

The Flight Data Acquisition System (FDAS) plays a critical role in aviation safety and performance monitoring. It is an essential component of an aircraft's avionics system, responsible for collecting and recording various flight parameters and operational data during the entire duration of a flight. The FDAS captures information such as altitude, airspeed, engine parameters, flight control inputs, and numerous other variables that provide valuable insights into aircraft operations. The FDAS is designed to meet stringent safety and reliability standards, ensuring accurate and real-time data acquisition under various flight conditions.

#### References

- [1] Ning Jia, Hang Chen, and Jun Tian, "A Design of Configurable Multi-type Flight Data Acquisition System," *IEEE International Conference on Signal Processing, Communication and Computing*, 2018. [CrossRef] [Google Scholar] [Publisher Link]

- [2] Guojin Peng, Wei Zhang, and Manting Liu, "A Method of Data Acquisition Network Delay Measurement for AFDX Avionics System in Flight Test," 7<sup>th</sup> International Conference on Signal and Image Processing, 2022. [CrossRef] [Google Scholar] [Publisher Link]

- [3] John W. Dyer et al., "Portable airborne Data Acquisition for Flight Testes," *IEEE International Instrumentation and Measurements Technology Conference Proceedings*, 2014. [CrossRef] [Google Scholar] [Publisher Link]

- [4] G.V. Jayaramaiah, and Chetan. Umadi, "FPGA Implementation of Multiprotocol Data Acquisition System using VHDL," *International Journal of Research in Engineering and Technology*, vol. 3, no. 7, pp. 390-394, 2020. [Google Scholar] [Publisher Link]

- [5] Ufuk Sakarya, Ibrahim Ayaz, and Ibrahim Hokelek, "Universal Verification Methodology Application of ARINC429 for Airborne Electronic Hardware Certification," 13<sup>th</sup> International Conference on Electrical and Electronics Engineering, 2021. [CrossRef] [Google Scholar] [Publisher Link]

- [6] K. Harikrishnan et al., "Sensor Data Acquisition and De-noising Using FPGA," *International Journal of Scientific and Engineering Research*, vol. 11, no. 8, 2020. [Publisher Link]

- [7] J. An, and S. Li, "Design of Architecture of Spaceflight Test Data Cen ters Using Cloud Platform," *Journal of Spacecraft TT&C Technology*, vol. 35, pp. 137-145, 2016. [Google Scholar]

- [8] Doug Laney, "3D Data Management: Controlling Data Volume, Velocity, and Variety," *META Group Research Note*, VOL. 6, NO. 70, 2001. [Google Scholar]

- [9] B. Zhao, Design and research of engine parameter collector system [D]. Xi'an, Northwestern Polytechnical University, 2018.

- [10] J. Zhang et al., "Hardware Design of Data Acquisition System for a Certain Aircraft Engine, Modern Electronics Technique," Xi'an, vol. 37, pp. 67-69, 2014.

- [11] Akwaowo U. Ekpa, Aniekan E. Eyoh, and Okon Ubom, "A Comparative Analysis of Volumetric Stockpile from UAV Photogrammetry and Total Station Data," *SSRG International Journal of Geoinformatics and Geological Science*, vol. 6, no. 2, pp. 29-37, 2019. [CrossRef] [Google Scholar] [Publisher Link]

- [12] M.K. Rachana, T.V. Sindhu, and Della Reasa Valiyaveetil, "Automatic Land surveillance System by Sketching Robot," *SSRG International Journal of Electronics and Communication Engineering*, vol. 3, no. 7, pp. 8-13, 2016. [CrossRef] [Publisher Link]

- [13] J. Zhang et al., "Hardware Design of Data Acquisition System for a Certain Aircraft Engine. Modern Electronics Technique," Xi'an, vol. 37, pp. 67-69, 2014.

- [14] Henrik Christophersen et al., "Small Adaptive Flight Control Systems for UAVs using FPGA/DSP Technology," *Georgia Institute of Technology*, 2004. [CrossRef] [Google Scholar] [Publisher Link]

- [15] J. Vignesh et al., "Digital Fuel Level Indicator for Motor Bikes using Arduino Microcontroller," SSRG International Journal of Electronics and Communication Engineering, vol. 4, no. 3, pp. 13-16, 2017. [CrossRef] [Google Scholar] [Publisher Link]

- [16] Ye Fan, "FPGA-Based Data Acquisition System," 2011 IEEE International Conference on Signal Processing, Communications and Computing (ICSPCC), 2011. [CrossRef] [Google Scholar] [Publisher Link]

- [17] Shi-zhen Huang, and Rui-Qi Chen, "FPGA- based IoT Sensor HUB," 2018 International Conference on Sensor Networks and Signal Processing (SNSP), 2018. [CrossRef] [Google Scholar] [Publisher Link]

- [18] Swarup S. Mathurkar et al., "Smart Sensor Based Monitoring System For Agriculture Using Field Programmable Gate Array," 2014 International Conference on Circuit, Power and Computing Technologies, 2014. [CrossRef] [Google Scholar] [Publisher Link]

- [19] Shuang Bao et al., "FPGA-Based Reconfigurable Data Acquisition System for Industrial Sensors," *IEEE Transactions on Industrial Informatics*, vol. 13, no. 4, pp. 1503-1512, 2017. [CrossRef] [Google Scholar] [Publisher Link]

## Pseudo Code

```

Design under Test

state<=0;

module

else

data_acq(adc_data,clk,reset,wr_en,rd_en,data_out);

begin

input [15:0] adc_data;

count<=16;

input clk,reset,wr_en,rd_en;

state<=0;

output reg[15:0] data_out;

end

reg [15:0] data, fifo data;

end

reg wr_en,rd_en;

default:state<=0;

spi

endcase

dut1(.adc_data(adc_data),.clk(clk),.reset(reset),.data(data));

end

assign data=mosi;

dut2(.data(data),.wr_en(wr_en),.rd_en(rd_en),.clk(clk),.reset(

endmodule

reset),.fifo_data(fifo_data));

module fifo(data,wr_en,rd_en,clk,reset,fifo_data);

ram

input [15:0] data;

dut3(.fifo data(fifo data),.clk(clk),.reset(reset),.wr en(wr en

input wr_en,rd_en,reset,clk;

),.rd_en(rd_en),.data_out(data_out));

output reg [15:0] fifo data;

endmodule

reg [15:0] data;

module spi(adc_data,clk,reset,data);

reg [4:0] rd_ptr, wr_ptr;

input [15:0] adc data;

input clk,reset;

reg [5:0]fifo cnt;

output reg [15:0] data;

reg [15:0] fifo_ram[128];

reg [4:0] count;

reg empty, full;

always@(data,wr en,rd en)

reg [15:0] mosi;

begin

reg cs 1;

if(wr en==1'b1)

//write into RAM

reg sclk;

begin

reg [2:0] state;

fifo_ram[wr_ptr]=data;

always@(posedge clk)

if(reset)

else if (rd_en==1'b1) // read from RAM

begin

begin

count<=5'd16;

fifo_data=fifo_ram[rd_ptr];

cs 1 <= 1'b1;

sclk <= 1'b0;

end

else

end

begin

else

fifo_data=fifo_data;

begin

case(state)

end

0:begin

always @( posedge clk )

sclk <= 1'b0;

begin: counter

cs 1 <= 1'b0;

if( reset )

mosi<=adc data;

count<=count-1;</pre>

fifo cnt \le 0;

else

state<=1:

begin

end

case ({wr_en,rd_en})

1:begin

2'b00 : fifo cnt <= fifo cnt;

sclk <= 1'b0;

2'b01 : fifo_cnt <= (fifo_cnt==0) ? 0: fifo_cnt-1;

if(count>0)

2'b10 : fifo_cnt <= (fifo_cnt==32) ? 32: fifo_cnt+1;

2'b11: fifo cnt <= fifo cnt;

```

default: fifo\_cnt <= fifo\_cnt;</pre>

```

endcase

//driver clocking block

end

//-----

end

clocking driver_cb @(posedge clk);

default input #1 output #1;

endmodule

endclocking

module ram(fifo_data,clk,reset,wr_en,rd_en,data_out);

input [15:0] fifo_data;

//-----

input clk,reset,wr_en,rd_en;

//monitor clocking block

output reg [15:0] data_out;

reg [4:0] wr ptr m,rd ptr m;

clocking monitor cb @(posedge clk);

reg [15:0] mem[(2**7):0];

default input #1 output #1;

always@(posedge clk)

endclocking

//-----

begin

if(reset==1'b1)

//driver modport

//-----

begin

for(int unsigned i=0;i<2**8;i++)

modport DRIVER (clocking driver_cb,input clk,reset);

begin

//monitor modport

mem[i] <= 0;

data out <= 0;

modport MONITOR (clocking

monitor cb,input

clk.reset):

end

endinterface

end

end

//-----

always@(fifo_data,wr_en,rd_en)

// sequence item

begin

//-----

if(wr_en==1'b1)

//write into RAM

class data_seq_item extends uvm_sequence_item;

begin

//-----

mem[wr_ptr_m]=fifo_data;

//data and control fields

else if (rd_en==1'b1) // read from RAM

//-----

bit

wr_en;

data_out=mem[rd_ptr_m];

rd en;

bit

rand bit [15:0] adc_data;

end

else

bit [15:0] data out;

//-----

begin

data out=data out;

//Utility and Field macros

//-----

end

`uvm_object_utils_begin(data_seq_item)

`uvm field int(adc data,UVM ALL ON)

endmodule

`uvm_object_utils_end

//-----

UVM Verification:

import uvm pkg::*;

//Constructor

`include "uvm macros.svh"

//----

//-----

function new(string name = "data seq item");

super.new(name);

endfunction

//

data interface

//-----

endclass

interface data_if(input logic clk,reset);

//-----

_____

//declaring the signals

// data sequence - random stimulus

//-----

logic wr en;

logic rd_en;

class

data_sequence

extends

logic [15:0] adc_data;

uvm_sequence#(data_seq_item);

logic [15:0] data_out;

`uvm_object_utils(data_sequence)

//-----

//-----

```

```

//Constructor

if(!uvm_config_db#(virtual data_if)::get(this, "", "vif",

//----

vif))

function new(string name = "data_sequence");

begin

`uvm error("build phase","driver virtual interface failed");

super.new(name);

endfunction

//-----

endfunction: build_phase

// create, randomize and send the item to driver

//-----

// run phase

//-----

task body();

virtual task run_phase(uvm_phase phase);

super.run phase(phase);

endtask

endclass

forever begin

data_seq_item trans;

//-----

seq_item_port.get_next_item(trans);

uvm_report_info("DATA_DRIVER ", $psprintf("Got

Transaction %s",trans.convert2string()));

sequencer

//-----

//-----

//Reading

data sequencer

extends

//-----

class

uvm_sequencer#(data_seq_item);

@(posedge vif.DRIVER.clk);

`uvm_component_utils(data_sequencer)

trans.data out=`DRIV IF.data out;

//-----

seq_item_port.item_done();

//constructor

end

//----

endtask: run_phase

//-----

function new(string name, uvm_component parent);

super.new(name,parent);

// drive - transaction level to signal level

// drives the value's from seq_item to interface signals

endfunction

function void build phase(uvm phase phase);

//-----

super.build_phase(phase);

endclass: data driver

endfunction

endclass

//-----

//

monitor

//-----

driver

//-----

`define MON_IF vif.MONITOR.monitor_cb

`define DRIV IF vif.DRIVER.driver cb

class data monitor extends uvm monitor;

class data_driver extends uvm_driver #(data_seq_item);

//-----

//-----

// Virtual Interface

//-----

// Virtual Interface

//-----

virtual data_if vif;

virtual data if vif;

//-----

`uvm_component_utils(data_driver)

// analysis port, to send the transaction to scoreboard

//-----

//-----

// Constructor

uvm_analysis_port

#(data_seq_item)

//-----

item_collected_port;

function new (string name, uvm_component parent);

//-----

// The following property holds the transaction

super.new(name, parent);

information currently

endfunction: new

// begin captured (by the collect_address_phase and

//----

data phase methods).

// build phase

//----

//-----

function void build_phase(uvm_phase phase);

`uvm_component_utils(data_monitor)

super.build_phase(phase);

//-----

// new - constructor

```

```

//-----

data_driver driver;

function new (string name, uvm component parent):

data sequencer sequencer;

super.new(name, parent);

data_monitor monitor;

item collected port = new("item collected port", this);

virtual data if vif;

endfunction

`uvm_component_utils_begin(data_agent)

//-----

`uvm_field_object(sequencer, UVM_ALL_ON)

// build_phase - getting the interface handle

'uvm field object(driver, UVM ALL ON)

`uvm_field_object(monitor, UVM_ALL_ON)

function void build_phase(uvm_phase phase);

'uvm component utils end

super.build phase(phase);

//-----

if(!uvm_config_db#(virtual data_if)::get(this, "", "vif",

// constructor

vif))

`uvm_error("build_phase", "No virtual interface

function new (string name, uvm_component parent);

specified for this monitor instance")

super.new(name, parent);

endfunction: build_phase

endfunction: new

//----

// run_phase - convert the signal level activity to

// build phase

//-----

transaction level.

//i.e., sample the values on the interface signal ans assigns

virtual function void build_phase(uvm_phase phase);

to transaction class fields

super.build phase(phase)

//-----

monitor = data_monitor::type_id::create("monitor",

this);

endclass: data_monitor

//creating driver and sequencer only for ACTIVE agent

driver = data_driver::type_id::create("driver", this);

class fun_cov extends uvm_subscriber#(data_seq_item);

sequencer

'uvm component utils(fun cov)

data sequencer::type id::create("sequencer", this);

data seg item trans;

uvm_config_db#(virtual data_if)::set(this, "seq", "vif",

covergroup cg:

vif):

WDATA:coverpoint trans.wr en { bins wd[16] =

uvm_config_db#(virtual data_if)::set(this, "driv", "vif",

{[0:2*16-1]}; }

vif);

RDATA:coverpoint trans.rd en { bins rd[16] = \{[0:2*16-1]\}

uvm_config_db#(virtual data_if)::set(this, "mon", "vif",

1]}; }

vif);

endgroup

if(!uvm_config_db#(virtual

data_if)::get(this,"","vif",vif))

function new(string name, uvm_component parent);

begin

super.new(name, parent);

`uvm_error("build_phase","agent virtual interface

cg = new();

endfunction //new()

failed");

function void build phase(uvm phase phase);

end

data_seq_item::type_id::create("trans");

endfunction: build_phase

trans

endfunction

//-----

function void write(data_seq_item t);

// connect_phase - connecting the driver and sequencer

this.trans = t;

port

cg.sample();

endfunction

function void connect phase(uvm phase phase);

endclass

super.connect phase(phase);

//-----

driver.seg item port.connect(sequencer.seg item export);

uvm_report_info("DATA_AGENT",

"connect phase,

Connected driver to sequencer");

agent

//-----

endfunction: connect phase

endclass: data agent

class data agent extends uvm agent;

//-----

//-----

// component instances

//-----

//

scoreboard

```

```

uvm_config_db#(virtual data_if)::set(this, "agt", "vif",

vif):

class data_scoreboard extends uvm_scoreboard;

uvm_config_db#(virtual data_if)::set(this, "scb", "vif",

//-----

vif);

if(! uvm_config_db#(virtual data_if)::get(this, "", "vif",

//port to receive packets from the monitor

//-----

vif))

uvm_analysis_imp#(data_seq_item,

data scoreboard)

item_collected_export;

`uvm_error("build_phase","Environment

virtual

interface failed")

`uvm component utils(data scoreboard)

data_seq_item trans;

end

//-----

endfunction: build_phase

//-----

// new - constructor

// connect_phase - connecting monitor and scoreboard

//-----

function new (string name, uvm_component parent);

//-----

super.new(name, parent);

function void connect_phase(uvm_phase phase);

item_collected_export=new("item_collected_export",this);

endfunction

super.connect_phase(phase);

//-----

agnt.monitor.item_collected_port.connect(scb.item_collected

// build phase - create port and initialize local memory

//-----

export);

function void build_phase(uvm_phase phase);

uvm_report_info("data_ENVIRONMENT",

"connect phase, Connected monitor to scoreboard");

super.build_phase(phase);

endfunction: connect_phase

endfunction: build phase

endclass: data env

//-----

// write task - recives the pkt from the monitor and pushes

//-----

into the queue

//----

//

endclass: data scoreboard

test

//-----

//-----

class data test extends uvm test;

`uvm_component_utils(data_test)

//

environment

//-----

//-----

// env instance

//-----

class data env extends uvm env;

data env env:

//-----

virtual data_if vif;

// agent and scoreboard instance

//-----

//-----

data_agent agnt;

// constructor

//-----

data_scoreboard scb;

function new(string name ,uvm_component parent);

virtual data_if vif;

super.new(name,parent);

'uvm component utils(data env)

endfunction: new

//-----

//-----

// constructor

//-----

// build phase

//-----

function new(string name, uvm_component parent);

function void build_phase(uvm_phase phase);

super.new(name, parent);

super.build phase(phase);

endfunction: new

// Create the env

//-----

env = data env::type id::create("env", this);

// build_phase - crate the components

uvm config db#(virtual data if)::set(this, "env", "vif",

//----

vif);

function void build_phase(uvm_phase phase);

if(! uvm config db#(virtual data if)::get(this, "", "vif",

super.build_phase(phase);

agnt = data_agent::type_id::create("agnt", this);

vif))

scb = data_scoreboard::type_id::create("scb", this);

begin

```

| `uvm_error("build_phase","Test virtual interface              | //                                                          |

|---------------------------------------------------------------|-------------------------------------------------------------|

| failed")                                                      | data_if intf(clk,reset);                                    |

| end                                                           | //                                                          |

| endfunction: build_phase                                      | //DUT instance                                              |

| task run_phase(uvm_phase phase);                              | //                                                          |

| data_sequence seq;                                            | data_acq DUT (                                              |

| <pre>seq = data_sequence::type_id::create("seq",this);</pre>  | .clk(intf.clk),                                             |

| <pre>phase.raise_objection(this,"starting main phase");</pre> | .reset(intf.reset),                                         |

| \$display("%t Starting sequence spi_seq run_phase",\$time);   | .wr_en(intf.wr_en),                                         |

| seq.start(env.agnt.sequencer);                                | .rd_en(intf.rd_en),                                         |

| #500ns;                                                       | .adc_data(intf.adc_data),                                   |

| <pre>phase.drop_objection(this,"finished main phase");</pre>  | .data_out(intf.data_out)                                    |

| endtask: run_phase                                            | );                                                          |

| endclass                                                      | //                                                          |

|                                                               | //passing the interface handle to lower heirarchy using set |

| //                                                            | method                                                      |

|                                                               | //and enabling the wave dump                                |

| // testbench.sv                                               | initial begin                                               |

| //                                                            | uvm_config_db#(virtual                                      |

| <del></del>                                                   | data_if)::set(uvm_root::get(),"*","vif",intf);              |

| module testbench_top;                                         | \$dumpfile("dump.vcd");                                     |

| always #5 clk = $\sim$ clk;                                   | \$dumpvars;                                                 |

| //                                                            | end                                                         |

| //reset Generation                                            | //                                                          |

| //                                                            | //calling test                                              |

| initial begin                                                 | //                                                          |

| reset = 1;                                                    | initial begin                                               |

| #15  reset = 0;                                               | run_test("data_test");                                      |

| end                                                           | end                                                         |

| //                                                            |                                                             |

| //interface instance                                          | endmodule                                                   |